Uncover & Solve SerDes Signal Integrity Challenges

Are you designing boards with high-speed chipsets, facing the critical task of maintaining reliable signal integrity as clock and data rates climb? The interconnect is part of your design, and so is the risk of costly re-spins. This essential webinar with Tektronix Senior Applications Engineer Dallas Mohler reveals how to quickly observe and debug real-world signal integrity issues that might plague SerDes links, ensuring faster time to solution.

Key insights you'll learn:

- Where and how to probe signals for meaningful insight

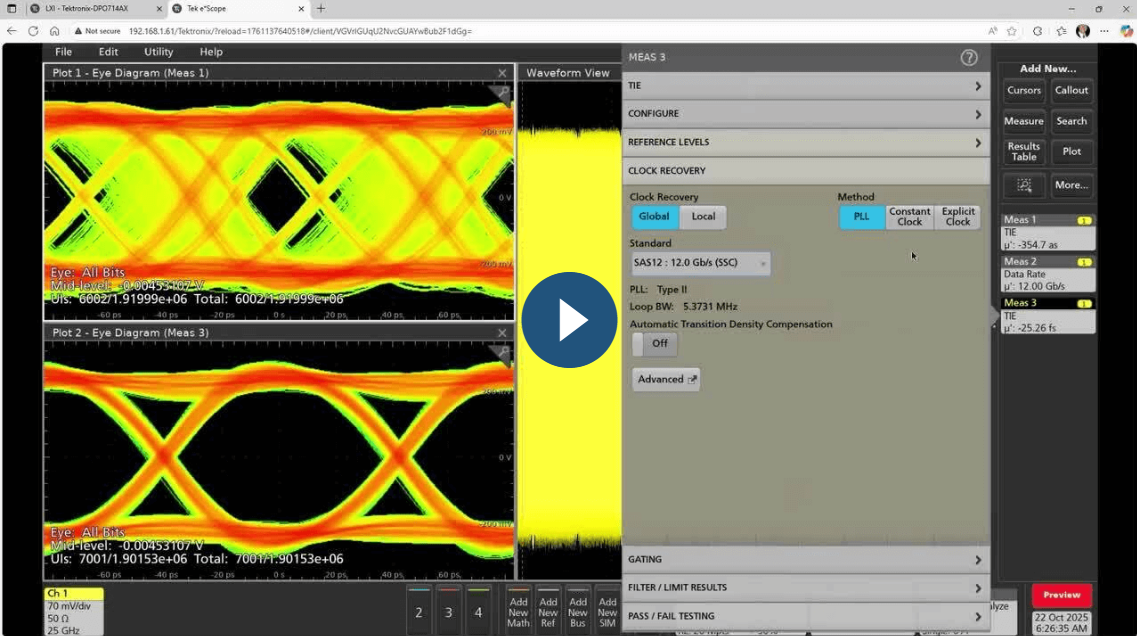

- How to set up clock recovery and when to apply equalization (CTLE/DFE)

- Methodologies to address closed eyes, random vs deterministic jitter, channel & signal path effects, and power rail induced noise.

Discover a repeatable debug workflow you can apply right away, resulting in fewer re-spins and faster bring-up.

Get more information about optimizing your high-speed serial data link designs.

Accelerate Your High-Speed SerDes Validation

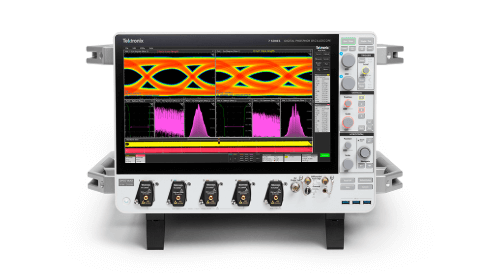

Designing high-speed standards (PCIe, Ethernet, MIPI) requires reliable validation tools to ensure minimal jitter and maximum eye opening. Our advanced real-time oscilloscopes, including the New 7 Series DPO, provide the necessary bandwidth, integrated jitter analysis, clock recovery, and equalization features (CTLE/DFE). These tools give engineers deep insight into channel effects, differentiating between deterministic and random noise sources. Stop wasting time on re-spins due to hidden SI issues.

Connect with our dedicated applications experts to discuss your specific chip-to-chip communication link challenges and learn how to implement a fully repeatable debug workflow in your lab.

Request for more details or talk to our experts today!

Download

Download Manuals, Datasheets, Software and more:

Feedback