Contact us

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

Tektronix at DesignCon 2026

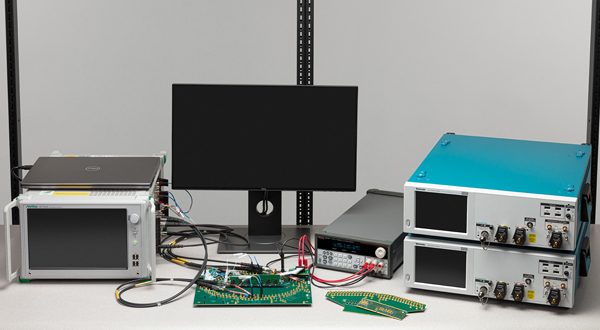

Tektronix will showcase advanced test and measurement solutions at DesignCon 2026, focusing on high-speed serial interfaces, signal and power integrity, and system-level validation.

Download our flyer and visit our booth to see live demonstrations and engage directly with Tektronix engineers working on PCI Express, DDR5, USB4 Version 2.0, AI power delivery, and solutions for next-generation signal integrity challenges.

Learn how to:

- Validate Signal Integrity Beyond the Measurement Path

- Gain Insight into Your PCI Express 7.0 SerDes Design

- Automate PCI Express 6.0 Compliance at 64 GT/s

- Evaluate Power Delivery Performance for High-Density AI Systems

- Streamline DDR5 DRAM Tx and Rx Compliance Testing

- Accelerate USB4 Version 2.0 Compliance at 40 Gbps Per Lane

- Simplify Multi-Port Power System Testing with Energy Recovery

Explore our Showcased Solutions

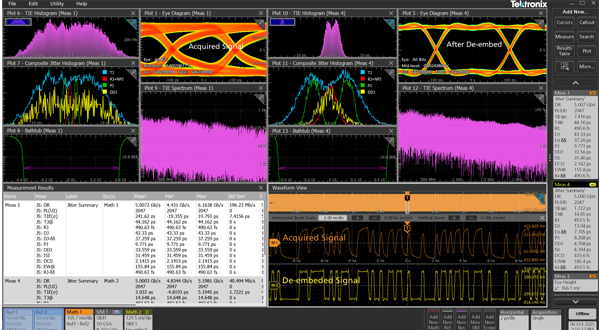

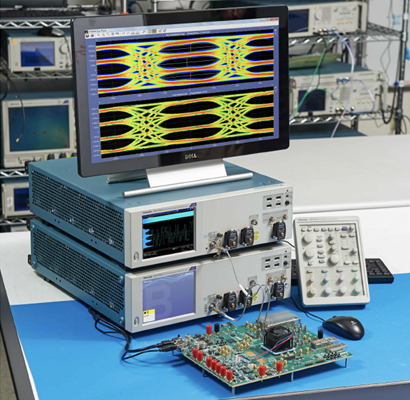

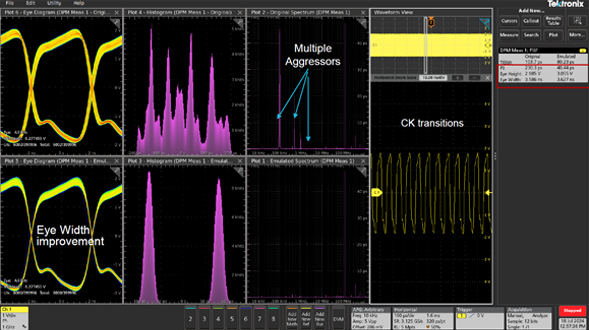

Validate Signal Integrity Beyond the Measurement Path

High-speed designs increasingly fail or pass due to limitations in the measurement setup rather than the device itself. Accurate validation requires separating true DUT behavior from probes, cables, fixtures, and interconnects that can obscure results.

Tektronix enables this by integrating signal integrity modeling, simulation, and equalization directly into the oscilloscope, reducing reliance on tools and manual workflows.

- Remove measurement artifacts through de-embedding to expose actual device performance

- Evaluate design tradeoffs by embedding real or hypothetical signal paths

- Measure realistic eye margins using transmitter and receiver equalization

- Compare multiple simulation scenarios directly on the oscilloscope

- Reduce false failures and avoid over-design driven by the test setup

Automate PCI Express 6.0 Compliance at 64 GT/s

Validating PCIe 6.0 at 64 GT/s requires repeatable workflows that reduce setup complexity while maintaining measurement confidence across transmitter and receiver testing.

Tektronix combines automated compliance software, high-performance oscilloscopes, and integrated debug tools to shorten validation cycles without sacrificing precision.

- Automate Tx and Rx compliance testing using guided, wizard-based workflows

- Reduce setup complexity and improve measurement consistency

- Validate backward compatibility at lower data rates

- Transition efficiently from compliance testing into detailed debugging using integrated analysis tools

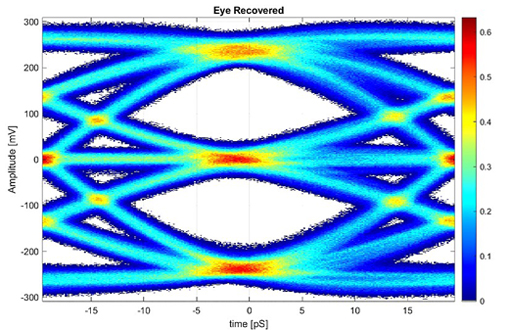

Gain Insight into Your PCI Express 7.0 SerDes Design

As data rates advance to 128 GT/s PAM4, validating signal integrity demands deeper visibility into noise, distortion, and equalization effects across the entire signal path.

Tektronix provides the bandwidth, noise performance, and analysis depth required to characterize next-generation SerDes behaviour before specifications and designs fully mature.

- Analyse PAM4 signalling at 128 GT/s including eye, jitter, SNDR, and RLM

- Verify transmitter electrical performance aligned to PCIe Base Specification 7.0

- Characterize and compensate measurement system noise

- Apply reference receiver equalization and channel embed and de-embed

Accelerate USB4 Version 2.0 Compliance at 40 Gbps Per Lane

USB4 Version 2.0 introduces PAM3 signalling at 40 Gbps per lane, increasing the need for accuracy, speed, and scalable data management during validation.

Tektronix enables high-throughput USB4 v2 validation by combining low-jitter measurement performance with automated workflows and centralized results management.

- Validate PAM3 signalling with automated USB4 v2 compliance testing

- Increase test throughput through parallel acquisition and analysis

- Improve accuracy with low intrinsic jitter performance

- Debug compliance failures in-house

- Manage results with centralized dashboards and reporting

Streamline DDR5 DRAM Tx and Rx Compliance Testing

DDR5 validation demands coordinated transmitter and receiver testing with flexibility to adapt workflows and accelerate root cause analysis.

Tektronix provides a unified compliance and debug environment that reduces handoffs between test phases and accelerates time to root cause.

- Validate DDR5 Tx and Rx performance using a standards-aligned workflow

- Reduce setup time with automated compliance execution

- Accelerate root cause analysis with flexible debugging tools

- Customize test plans for device- and system-specific requirements

- Gain deeper visibility into signal behavior

Evaluate Power Delivery Performance for High-Density AI Systems

AI servers place extreme demands on power delivery networks, combining high current, fast load steps, and time-variant behavior that must be validated under realistic operating stress.

Tektronix measurement solutions deliver the bandwidth, dynamic range, and probing fidelity required to observe PDN behavior that traditional methods often miss.

- Capture high-current, nanosecond-level transients with low noise

- Assess stability of large-signal, time-variant power delivery networks

- Validate ultra-low impedance under real-world load conditions

- Correlate electrical measurements with system-level behavior

- Identify power integrity risks before deployment

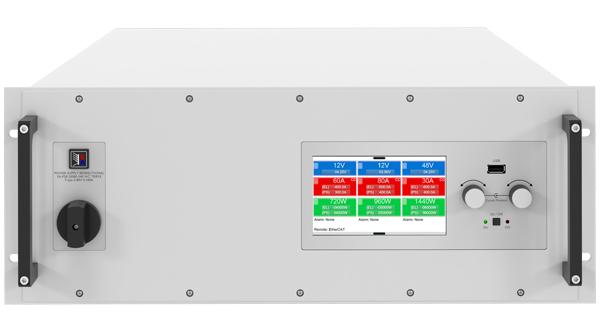

Simplify Multi-Port Power System Testing with Energy Recovery

Validating complex power systems requires flexible control, fast response, and efficient energy handling across multiple channels.

Tektronix bidirectional power platforms combine multi-channel control, fast transient response, and energy recovery to enable scalable system-level testing with lower lab overhead.

- Independently control three isolated bidirectional DC channels up to 10 kW each

- Correlate electrical and thermal performance using direct temperature sensing

- Execute fast transients and closed-loop tests with 1 ms communication speed

- Recover up to 96 percent of energy during sink operation to reduce lab power and heat