Contact us

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

PCIe Gen 5 Transmitter

Compliance Testing

Adaptive Solutions for Advancing Standards

Rapidly advancing technologies and increasingly high signal speeds in data centers, enterprise cloud, and high-speed networking all require higher transfer rates (32.0 GT/s for Gen 5) while maintaining an acceptable level of signal integrity.

Tektronix’s PCIe Gen 5 solution enables you to test your transmitter across x1, x4, x8, or x16 links with flexible test configurations and comprehensive reporting. It’s designed for fast, reliable:

- Debugging

- Validation

- Compliance testing against the PCI-SIG specification

The TekExpress test automation framework evolves with the standards, using methodologies rigorously tested by industry leaders to help you achieve accurate results the first time through.

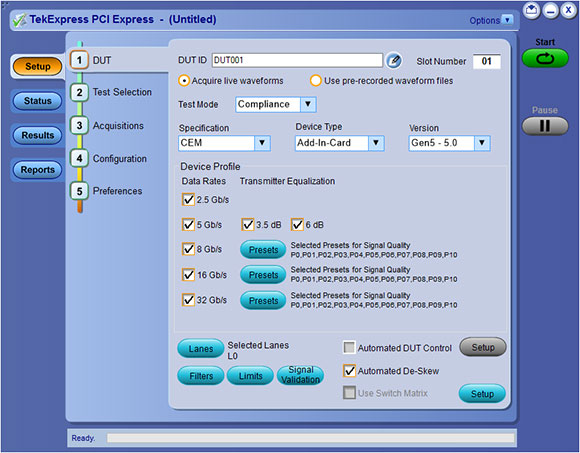

Save Time and Reduce Errors with Automation

TekExpress PCIe 5.0 Tx automation software:

- Autonomously steps the DUT through different speeds, patterns, and Tx EQ presets

- Verifies the correct signal at the transmitter before taking measurements

- Performs channel and package embedding and de-embedding

- Supports legacy SigTest and SigTest Phoenix software versions and template files

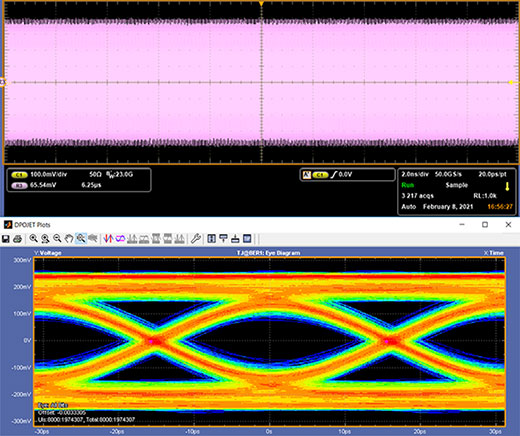

- Performs 100 MHz reference clock jitter and signal integrity measurements with Silicon Labs “PCIe Clock Jitter Tool” and Tektronix DPOJET software

Stay Ahead with Tektronix Gen 5 Pre-Compliance Fixtures

While the PCI Express 5.0 Integrators List (compliance) program is still under development, the industry has rapidly adopted Gen 5 technology. Tektronix has developed non-compliance PCI Express 5.0 CEM test fixtures to help you keep your project moving forward until fixtures are available from the PCI-SIG. Tektronix pre-compliance fixtures can be used for transmitter testing from 2.5 GT/s to 32.0 GT/s, receiver testing at 32.0 GT/s, refclk jitter and AC testing, and add-in card PLL bandwidth testing.

Optimized Reference Clock Jitter Testing

With Gen 5’s maximum data rate extending to 32.0 GT/s, it’s crucial to be as precise as possible characterizing PCIe 100 MHz refclk drivers and delivery mechanisms. Higher bandwidths are made possible through a series of technological advancements and trade-offs including dropping the allowed jitter limit for refclks. This trend is expected to continue as the PCI-SIG continues progressing to 6.0 specifications. As measurement methodologies become increasingly complex, our PCIe Gen 5 Solution manages the necessary intricacies so engineers can make data-driven enhancements to their designs.