Contact us

Call

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

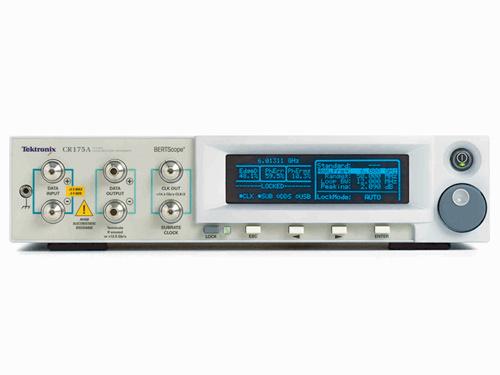

BERTScope CR (Discontinued)

This product has been discontinued.

There is no direct replacement for the BERTScope CR.

Technical documents and product support for current BERTScope CR owners can be found at the links below.

BERTScope CR