お問い合わせ

ダウンロード

マニュアル、データシート、ソフトウェアなどのダウンロード:

フィードバック

HPCアーキテクチャの検証

当社のソリューションが、周波とデータレートのスケーリングにおける信号および電源の完全性テストの高速化、高メモリ周波向けDDRアーキテクチャの検証、そしてJEDEC準拠の実現にどのように役立つかをご覧ください。

AIデータセンタ・テスト・アプリケーション

信号完全性測定とモデリング

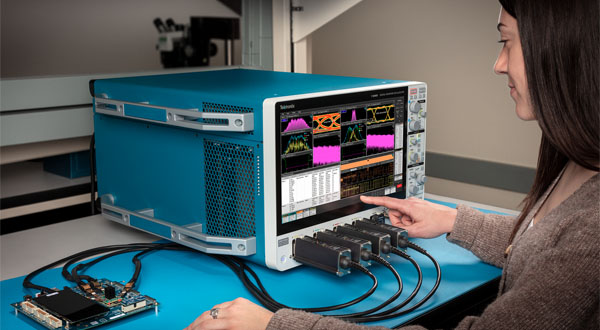

テクトロニクスのオシロスコープは、シグナル・インテグリティ・モデリング(SIM)と組み合わせることで、測定経路の影響を除去し、実際のチャンネル条件を組み込み、複雑なPCB相互接続を介して信号がどのように伝搬するかをシミュレートできます。これらすべては計測器上で直接行うことができます。拡張SIM (SIMA) を使用すると、受信機イコライゼーション (CTLE、FFE、DFE) や送信機プリエンファシス/デエンファシスなどの強力なイコライゼーション モデリングが可能になり、困難な高速環境における設計上のトレードオフを、より深く理解し、検討することができます。

これらのツールは、高度なジッタ解析およびアイ・ダイアグラム解析オプション(例:DJA)と連携して動作し、確定ジッタとランダム・ジッタの影響を分解し、設計マージンを維持しながら準拠性を検証します。

電力供給ネットワーク(PDN)の検証

AI設計には、極めて堅牢な電力供給の安定性も必要になります。1V以下の電圧で数百アンペアの電流を、最小限のノイズと過渡的外乱で供給することは、確実な性能を実現する上で不可欠です。テクトロニクスのオシロスコープとプローブは、PDNのインピーダンスと過渡特性の評価、大電流レールの測定と解析、および電力イベントとデータパスの動作との相関関係の把握を可能にします。

限られた時間枠内でマスクのコンプライアンスを達成

テクトロニクスのソリューションは、エンジニアが高速メモリ・インタフェース上でDDRタイミング・マージンを直接測定および検証できる機能を提供します。高度なアイダイアグラムとタイミング解析を用いることで、設計者は、実際のチャンネル損失、反射、相互接続のばらつきを考慮しながら、信号がJEDECで定義されたマスク内に収まるようにすることができます。これは、メモリ速度の向上に伴い、データの整合性とシステムの信頼性を維持するために非常に重要です。

トランスミッタおよびレシーバのコンプライアンス・テスト

テクトロニクスのオシロスコープと自動化されたDDR準拠ワークフローを組み合わせることで、DDRトランスミッタとレシーバの両方の検証プロセスが簡素化されます。

エンジニアは、TXコンプライアンス・テストを実行して、メモリ・モジュールが要求された電圧とタイミングの範囲内で信号を駆動していることの確認や、RXコンプライアンス・テストを実行して、メモリコントローラが最悪の条件下で受信データを正しくサンプリングしていることの検証が可能です。