與我們聯絡

與 Tek 業務代表即時對談。 上班時間:上午 6:00 - 下午 4:30 (太平洋時間)

致電

請致電

與 Tek 業務代表即時對談。 上班時間:上午 8:30 - 下午 5:30 (太平洋時間)

下載

下載手冊、產品規格表、軟體等等:

意見回饋

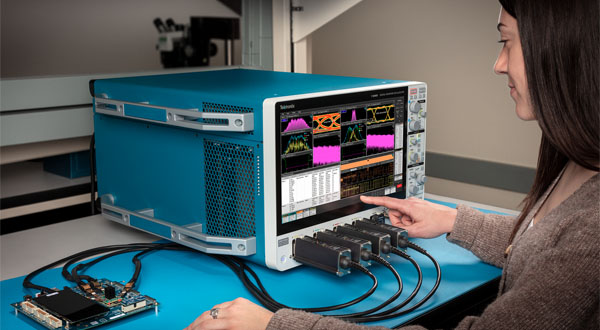

驗證 HPC 架構

探索我們的解決方案如何協助您加速測試頻寬和資料速率擴充的訊號和電源完整性,以及驗證高記憶體頻寬的 DDR 架構,並確認符合 JEDEC 規範。

AI 資料中心測試應用

供電網路 (PDN) 驗證

AI 設計也需要堅如磐石的電源完整性。在 1 V 以下的電壓軌上提供數百安培的電流,並將雜訊和暫態干擾降至最低,是達成穩定效能的基本條件。泰克示波器和探針可進行 PDN 阻抗和暫態特性分析、大電流軌路測量和分析,以及電源事件與資料路徑行為的關聯。

在緊迫的時間窗內實現掩膜合規性

Tektronix 解決方案提供工程師直接在高速記憶體介面上量測與驗證 DDR 時序裕度的能力。利用先進的眼圖和時序分析,設計人員可以確保訊號保持在 JEDEC 定義的遮罩範圍內,同時考慮到實際世界中的通道損耗、反射和互連變化。隨著記憶體速度的提升,這對於維持資料完整性和系統可靠性至關重要。

發射器與接收器符合性測試

泰克示波器結合自動化 DDR 相容工作流程,可簡化 DDR 發射器和接收器的驗證流程。

工程師可以執行 TX 符合性測試 - 確保記憶體模組在所需的電壓和時序視窗內驅動訊號,並執行 RX 符合性測試 - 以驗證記憶體控制器是否能在最惡劣的情況下正確取樣輸入資料。