연락처

텍트로닉스 담당자와 실시간 상담 6:00am-4:30pm PST에 이용 가능

전화 문의

9:00am-6:00PM KST에 이용 가능

다운로드

매뉴얼, 데이터 시트, 소프트웨어 등을 다운로드할 수 있습니다.

피드백

HPC 아키텍처 검증

키사이트 솔루션이 대역폭 및 데이터 속도 확장을 위한 신호 및 전력 무결성 테스트와 높은 메모리 대역폭을 위한 DDR 아키텍처 검증 및 JEDEC 규정 준수를 가속화하는 데 어떻게 도움이 되는지 알아보세요.

AI 데이터 센터 테스트 애플리케이션

신호 무결성 측정 및 모델링

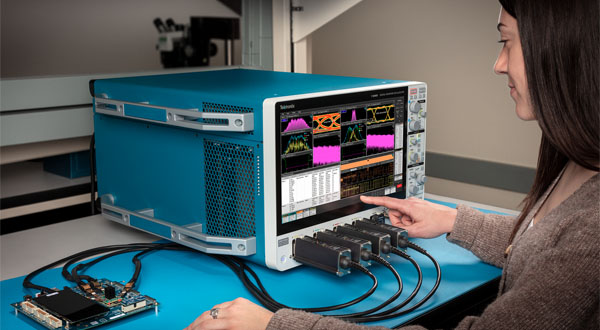

신호 무결성 모델링(SIM)과 함께 텍트로닉스 오실로스코프를 사용하면 측정 경로 효과를 제거하고 실제 채널 조건을 포함하며 복잡한 PCB 상호 연결을 통해 신호가 어떻게 전파되는지 시뮬레이션할 수 있으며 이 모든 작업을 계측기에서 직접 수행할 수 있습니다. SIM Advanced(SIMA)를 사용하면 수신기 이퀄라이제이션(CTLE, FFE, DFE) 및 송신기 프리 엠퍼시스/디엠퍼시스 등 강력한 이퀄라이제이션 모델링을 통해 까다로운 고속 환경에서 눈을 뜨고 설계 절충점을 탐색할 수 있습니다.

이러한 도구는 고급 지터 및 아이 다이어그램 분석 옵션(예: DJA)과 함께 작동하여 결정론적 및 무작위 지터 효과를 분석하고 설계 마진을 보존하면서 규정 준수 여부를 검증합니다.

전력 전송 네트워크(PDN) 유효성 검사

AI 설계에는 견고한 전력 무결성도 필요합니다. 노이즈와 과도 장애를 최소화하면서 1V 미만의 레일에서 수백 암페어를 제공하는 것은 결정론적 성능을 위한 기본입니다. 텍트로닉스 오실로스코프와 프로브는 PDN 임피던스 및 과도 특성화, 고전류 레일 측정 및 분석, 데이터 경로 동작과 전력 이벤트의 상관관계를 지원합니다.

촉박한 시간 내에 마스크 규정 준수 달성하기

텍트로닉스 솔루션은 엔지니어가 고속 메모리 인터페이스에서 직접 DDR 타이밍 마진을 측정하고 검증할 수 있는 기능을 제공합니다. 설계자는 고급 아이 다이어그램 및 타이밍 분석을 사용하여 실제 채널 손실, 반사 및 상호 연결 변수를 고려하면서 신호가 JEDEC 정의 마스크 내에 유지되도록 할 수 있습니다. 이는 메모리 속도가 확장됨에 따라 데이터 무결성과 시스템 안정성을 유지하는 데 매우 중요합니다.

송신기 및 수신기 컴플라이언스 테스트

자동화된 DDR 컴플라이언스 워크플로와 결합된 텍트로닉스 오실로스코프는 DDR 송신기와 수신기를 모두 검증하는 프로세스를 간소화합니다.

엔지니어는 메모리 모듈이 필요한 전압 및 타이밍 윈도우 내에서 신호를 구동하는지 확인하는 TX 컴플라이언스 테스트와 메모리 컨트롤러가 최악의 조건에서 수신 데이터를 올바르게 샘플링하는지 확인하는 RX 컴플라이언스 테스트를 실행할 수 있습니다.