Contact us

Live Chat with Tek representatives. Available 6:00 AM - 4:30 PM

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

Kiểm tra và gỡ lỗi tự động

Các tiêu chuẩn kỹ thuật số tốc độ cao đang phát triển nhanh chóng để hỗ trợ nhu cầu về hiệu suất của thế giới vận hành bằng dữ liệu của chúng ta. Các tiêu chuẩn nối tiếp thế hệ tiếp theo và các yêu cầu giao tiếp dữ liệu mang đến những thách thức mới trong hoạt động kiểm tra, đẩy các giới hạn của công cụ gỡ lỗi và tuân thủ ngày nay. Từ thiết kế và mô phỏng, phân tích, gỡ lỗi và kiểm tra tuân thủ, Tektronix cung cấp các giải pháp kiểm tra điện tự động để tối ưu hóa hiệu suất, tăng tốc chu kỳ xác nhận và rút ngắn thời gian đưa sản phẩm ra thị trường.

Kiểm tra chính xác, có thể lặp lại các tiêu chuẩn điện toán hiệu suất cao

Nhu cầu thông lượng dữ liệu lớn hơn và dung lượng bộ nhớ tăng lên tiếp tục tăng trong các thị trường sử dụng nhiều dữ liệu như trung tâm dữ liệu, trí tuệ nhân tạo (AI) và điện toán hiệu suất cao. Tốc độ truyền dữ liệu cao hơn dẫn đến các thiết kế phức tạp đẩy ranh giới của tính toàn vẹn tín hiệu và yêu cầu các phép đo hiệu suất cao hơn để tuân thủ, gỡ lỗi và xác thực. Các giải pháp kiểm tra tự động của Tektronix trang bị cho các kỹ sư kiểm tra những thiết kế mới nhất của họ bằng cách giải quyết những thách thức này với độ chính xác và khả năng lặp lại.

Giảm thời gian để kiểm tra công nghệ tiêu dùng

Tốc độ đổi mới đang kích thích nhu cầu về các thiết bị tiêu dùng mới hơn và nhanh hơn. Các tiêu chuẩn làm cơ sở cho sự phát triển những thiết bị này đặt ra những thách thức kiểm tra mới về tốc độ dữ liệu và độ phức tạp của thiết kế tăng lên. Các giải pháp kiểm tra của Tektronix cung cấp các phép đo chính xác, có thể lặp lại và giảm thời gian kiểm tra để tuân thủ các thông số kỹ thuật mới nhất.

Màn hình (DisplayPort và HDMI)

Công cụ toàn diện cho thiết kế thiết bị Ethernet

Ethernet cung cấp khả năng kết nối mạng từ các trung tâm dữ liệu siêu quy mô và hệ thống doanh nghiệp đến các ứng dụng ô tô và công nghiệp. Tektronix cung cấp các bộ công cụ toàn diện để kiểm tra, phát triển và gỡ lỗi lớp vật lý của thiết bị Ethernet IEEE 802.3 trong các hệ sinh thái này.

Công cụ đo lường và phân tích tính toàn vẹn tín hiệu nâng cao

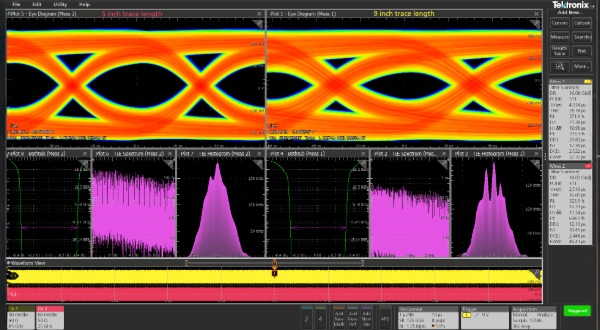

Tektronix cung cấp một bộ công cụ phân tích mạnh mẽ cho các chuẩn nối tiếp tốc độ cao hiện nay – được thiết kế để xử lý các cấu hình phức tạp, đa nguồn với tốc độ và sự linh hoạt.Với quy trình làm việc trực quan, khả năng đo lường mật độ cao và khả năng trực quan hóa hàng đầu trong ngành, các công cụ của Tektronix giúp kỹ sư phân tích nhiều dữ liệu hơn, dễ dàng hơn và trong thời gian ngắn hơn.

Phân tích Jitter và Biểu đồ Mắt (tùy chọn DJA)

Khử nhúng, Nhúng và Cân bằng tín hiệu (tùy chọn SIM Nâng cao)

Đối với băng thông trên 25 GHz, DPOJET, PAMJET và SDLA vẫn có sẵn trên nền tảng DPO70000 Series để hỗ trợ các trường hợp sử dụng băng thông cao.