お問い合わせ

ダウンロード

マニュアル、データシート、ソフトウェアなどのダウンロード:

フィードバック

エキスパートが簡単に解決。

テクトロニクスは、お客様チームのサポートとして、時間、コストを節約し、電子テスト/計測機器の確度を保証する、カスタマイズされた機器校正サービス・ソリューションを提供しています。当社はお客様と協力して、高度なT&M機器の校正を強化または外注する際の賢明な経営判断をサポートします。 多くの企業が、競争力のある市場価格でOEM品質の機器校正を提供するテクトロニクスを信頼しています。

- テクトロニクス、ケースレー、フルーク、Keysight、Rohde & Schwartz、Agilent、その他9000社を超えるT&M機器メーカに対応

- カスタマイズされたプログラムオプション:オンサイト、現地拠点から工場へ出荷

- 迅速で信頼性の高いターンアラウンド・タイム

- Z540およびISO 17025認定機器校正の全範囲

- A2LA認定技術者

エキスパートが簡単に解決。

テクトロニクスは、お客様チームのサポートとして、時間、コストを節約し、電子テスト/計測機器の確度を保証する、カスタマイズされた機器校正サービス・ソリューションを提供しています。当社はお客様と協力して、高度なT&M機器の校正を強化または外注する際の賢明な経営判断をサポートします。 多くの企業が、競争力のある市場価格でOEM品質の機器校正を提供するテクトロニクスを信頼しています。

- テクトロニクス、ケースレー、フルーク、Keysight、Rohde & Schwartz、Agilent、その他9000社を超えるT&M機器メーカに対応

- カスタマイズされたプログラムオプション:オンサイト、現地拠点から工場へ出荷

- 迅速で信頼性の高いターンアラウンド・タイム

- Z540およびISO 17025認定機器校正の全範囲

- A2LA認定技術者

Customized Wafer Probing

Tektronix employs a team of electrical and mechanical design engineers that can develop customized wafer probe cards and test solutions to meet the most demanding requirements.For projects requiring wafer processing (e.g., wafer bumping, thinning, dicing), we maintain relationships with a variety of domestic and international industry suppliers and offer supply chain management capabilities to enable a turnkey solution for your microelectronic parts.

Understanding Wafer Testing: Ensuring Quality in Semiconductor Manufacturing

Wafer Test (also referred to as Wafer Probe) is a vital step in the Semiconductor Value Stream, focusing on electrical screening and consumption of Known Good Die (KGD). It involves probing individual semiconductor devices on a wafer to identify defects and confirm functionality before further manufacturing.

What does wafer testing entail?

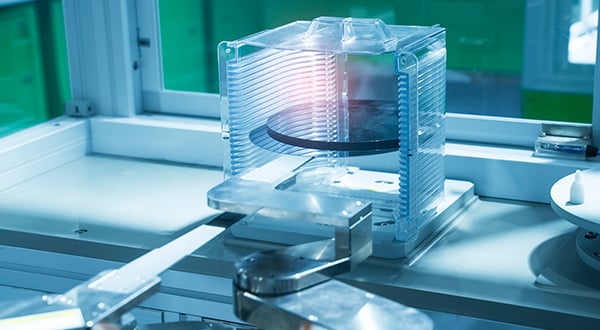

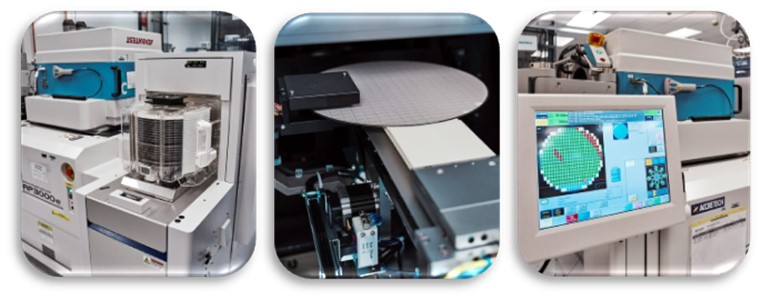

First let's start with understanding the form-factor of a modern wafer. A wafer is basically a disc that is no greater than 3/4 mm thick and up to 300 mm in diameter. To put this into perspective, imagine a silicon disc that is half the thickness of a dime and a foot in diameter. Due to the form-factor and fragile nature of the wafer, it is not practical to process a wafer by hand (not to mention that most wafers are bumped). So, in today’s semiconductor testing environment fully automated equipment is utilized to enable the process. The automation includes both a wafer prober to handle, a programmed test solution to perform the electrical testing, and robotic equipment to perform inspection and sort wafers.

To make a connection to the Device Under Test (DUT), a probe head and card must be designed (typically unique to each Integrated Circuit - IC) and integrated with the test station and wafer prober to form the test solution.

A cassette of wafers (up to 25 at a time) are loaded onto the prober and the process of screening wafers starts. An individual wafer is selected, placed on a stage, and is manipulated such that each device on the wafer can be accessed and electrically tested. The data for each IC is then collected and a digital map is generated identifying the location and Pass/Fail status. Once complete, the wafer(s) can be sent on to the dicing process step so that the KGD are ready to be consumed at the next level.

What are the benefits of wafer test?

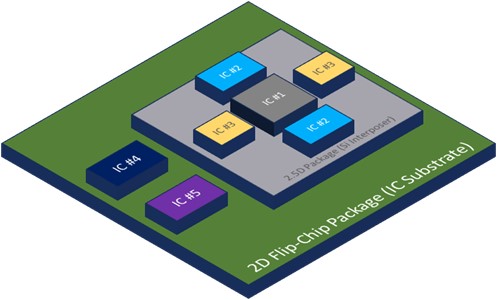

In the era of System on a Chip (SOC) and Heterogeneous Solutions, where integrating multiple complex ICs per package is the norm, the significance of KGD entering the packaging stage cannot be overstated. Wafer Test plays a crucial role in defect detection, ensuring that non-conforming components are identified and prevented from reaching the next stage of production. Paired with continuous Process Monitoring, it empowers engineers to address issues at an early stage, significantly contributing to yield improvement and reduced production costs by eliminating defects in the early steps of the Semiconductor Value Stream.

Request More Information

Wafer Probe FAQs

What is the common testing frequency ranges?

What is the common testing temperature ranges?

The test solutions are configured to support common temperatures of -40°C, +100°C, +125°C with room temperature (25°C to 40°C).

Specifically, the prober TEL P8XL model can reach temperatures as low as -55°C, while the Accretech model is capable of going down to -40°C.

What are some of challenges wafer testing faces today?

Since wafer testing is a complex service, I will only highlight a few challenges that are top of mind.

First off, the prevalence of heterogeneous solutions, where multiple devices are integrated into a single package, introduces complexities in tracking and managing these components throughout the testing process. This necessitates robust part identification and traceability systems to ensure the integrity of each element.

Secondly, the shift towards 2.5D solutions has significantly increased the interconnect density for a given Integrated Circuits (ICs). For example, the interconnect spacing on an IC could shrink from 0.150 mm to 0.030 mm. That is a 5X decrease on both the X- and Y-axis leading to an interconnect density increase of up to 25X. With such tight spacing and planarity requirements, new probing solutions and methods must be developed and qualified.

Lastly, as the demand for IC solutions expands, so does the demand on wafer testing. To eliminate opportunities for defects caused by handling, the need to eliminate manual handling is paramount.

What are some the opportunities for improvement?

To enhance traceability in wafer testing, integrating non-volatile memory directly into the IC design (rather than laser scribing human readable unique identifiers) allows for accuracy and ease of tracking. With this in place it is easy to capture wafer lot, wafer number, and row/column information for each IC, contributing to improved part genealogy and tracking throughout the manufacturing process. By leveraging non-volatile memory, the semiconductor industry can fortify its traceability mechanisms, ensuring that IC traceability is maintained beyond the Semiconductor Value Stream.

As the semiconductor industry evolves to incorporate 2.5D solutions, the increased interconnect density on ICs poses a new challenge. Addressing this calls for innovative probing solutions requiring increase collaboration between test providers, wafer test equipment vendors, and probe solutions suppliers. By working together, advanced probing methods that can adeptly manage the tighter spacing and heightened planarity requirements associated with this shift.

The demand for comprehensive automation in wafer testing is a critical avenue for improvement. These systems that can efficiently eliminate human handling steps leading to the reduction in unwanted defects and enhancing overall efficiency in the testing environment. By combining AI & Machine Learning to the inspection process, screening can be enhanced to improve screening time and effectiveness, addressing challenges associated with human-dependent procedures.

What is the future of wafer test?

What are some common wafer probe applications?

Wafer probing is commonly used in the semiconductor industry for a variety of applications, including process control, device characterization, failure analysis, and reliability testing.

What are some types of wafer probes?

There are several types of wafer probes, including manual probes, semi-automatic probes, and fully automatic probes. Manual probes require an operator to manually move the wafer to each test site, while semi-automatic and fully automatic probes can automatically move the wafer to each test site.

What are some factors to consider when selecting a wafer probe?

When selecting a wafer probe, it is important to consider factors such as probe tip size and shape, probe tip material, probe planarity, and probe placement accuracy. Other factors to consider include the number of probes, the size of the wafer, and the required throughput.