Steve Sandler, President of Picotest, as well as Maria Agoston, Cameron Lowe, Tony Ambrose, all of Tektronix, also contributed to this blog.

Why You Should Care About Jitter

Jitter is a common problem. A quantified misplacement in time of the signal relative to the expected time position, jitter is ultimately a degradation of the key definition of performance of a serial link, which is the bit error ratio. Power distribution networks (PDNs) can cause noise as well as jitter; both can cause transmission errors and increase the bit error ratio of a serial link.

Engineers need to characterize their devices definitely in terms of the bit error ratio. They want to know whether their device is measuring up to the target bit error ratio, whether it has forward error correction, and what is the target bit error ratio they need to reach. The behavior of different elements is very relevant to the total behavior and impairment of a device.

Traditionally, Bit Error Rate Testers (BERTs) were used as instruments to directly measure the bit error ratio, which is the actual measurement target, but those devices are very expensive, and they don't really help people identify the root causes of impairments of the links. As a result, the industry developed alternate approaches using oscilloscopes and advanced custom analysis tools, which are better focused on the causes of error, are more cost-effective and have faster throughput. Bit error requirements have been translated to jitter and noise budgets.

Consider a serial link with a transmitter, channel, and receiver. From the receiver's point of view, we can see that the decision threshold is impaired by the noise in the system, and the time reference is impaired by jitter. By extracting jitter and noise and identifying them clearly in a serial link, we can extrapolate their effects to predict the bit error ratio and understand the performance of the system. Jitter analysis evaluates a waveform in the horizontal dimension based on when the waveform crosses a horizontal reference line, while noise analysis evaluates along a vertical dimension on the basis of crossings of a vertical reference line, typically in the center of the eye; combining jitter and noise analysis provides a better prediction of bit error ratio performance.

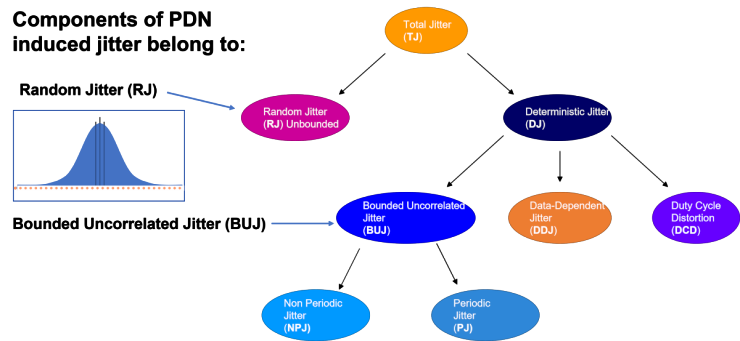

Types of Jitter

Jitter is caused by many things, including:

- Broadband noise density jitter: Wideband noise related to power loss impedance that shows up as voltage in sensitive circuits, creating jitter.

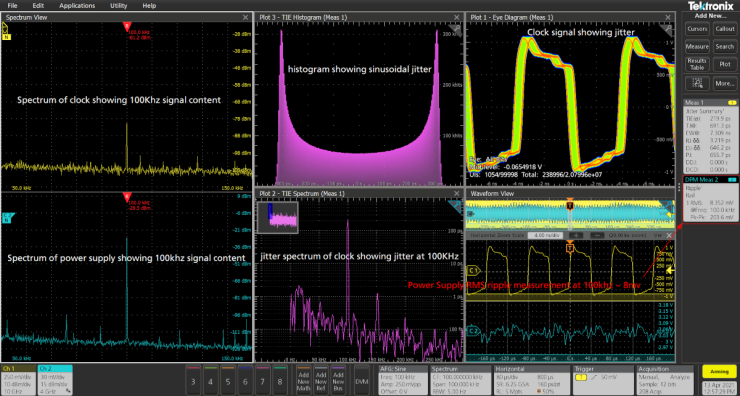

- Power rail resonance jitter: Impedance resonance, with noise peaks that convert to AM in the power supplier rail of a sensitive circuit.

Image 1: Example of Power Rail Resonance Jitter

- Event-driven jitter: Jitter that occurs because of something else that happened in the system.

- Modulation-induced jitter: FM or phase modulation that converts to AM on the power supply rail.

- Thermal noise: Typically a Gaussian distribution, thermal (or intrinsic) noise is unbounded and caused by the random thermal motion of carriers. It’s much like background conversations … random and ever-changing.

- Injected noise: Jitter from electromagnetic interference (EMI) or crosstalk from neighboring wiring, injected noise is bounded but uncorrelated to the data stream the device is handling. It usually has a fixed, identifiable source, like an oscillator or power supply.

Image 2: Example of Jitter on Clock from Power Supply

- Transmission losses: Jitter due to bandwidth limitations, skin effect losses, dielectric absorption, dispersion in the optical fiber, or reflections, impedance and mismatches.

How to Analyze Jitter and Noise

The goal is to predict, using limited acquired data, the behavior of a device at target bit error ratio specifications. The methods are complex, requiring the tester to decompose, reconcile and model noise and jitter. It involves a five-step process:

- Acquire statistically relevant data. How to do so depends on whether the oscilloscope in use is a real-time or a sampling instrument.

- Break down and separate the various jitter and noise components.

- Reconcile the effects of jitter and noise. What is jitter? What is noise? Noise is always jitter, but jitter is not always noise.

- Build statistical models that allow for extrapolation of behaviors to higher BER targets.

- Perform measurement on the models for Total Jitter as a Specified Bit Error Rate (TJ@BER) and Total Noise at a Specified Bit Error Rare (TN@BER).

The serial data standards of today’s high-speed communications require extensive jitter compliance tests. Learn more about how Tektronix' test instrumentation portfolio enables you to meet design goals and compliance requirements or view our on-demand webinar, Signal and Power Integrity.