本アプリケーション・ノートの概要

- クロック信号のシンプルなタイミング解析測定手順を説明します。

- タイミング/ジッタ測定の解釈の仕方について説明します。

- 非変調のクロック、スペクトラム拡散クロック、組込みクロックのシリアル・データ、クロック・データの測定例を説明します。

- 拡張ジッタ測定によって改善されるタイミング特性評価とトラブルシュートについて説明します。

5シリーズMSOは、標準の測定機能とオプションの拡張ジッタ解析機能を装備した、組込みシステム設計におけるタイミング・ジッタの特性評価とトラブルシュートのための強力なツールです。

はじめに

クロックは組込みシステムの心臓部であり、コンポーネント、サブシステム、システム全体の間のタイミング基準と同期をつかさどります。クロック信号の崩壊、歪みはシステム動作の低下または断続の原因になることがあるため、クロック信号の十分な特性評価は、信頼できる組込みシステム設計において欠かせない手順です。

ジッタは、クロック回路の性能を表す一般的な指標です。簡単に言うと、ジッタは本来あるべき信号エッジからのタイミング偏差です。ジッタの特性評価には、さまざまな測定があります。

このアプリケーション・ノートでは、5シリーズMSOの標準およびオプションの測定機能を使用したジッタ測定をいくつかご紹介します。

クロック・ジッタの特性評価

標準の自動測定

標準の自動測定機能を使用して、クロックの周波数が 仕様を満たしていることを確認することからジッタ解 析を始めます。次に、周波数の最小値、最大値など の統計測定により、クロック・パルスが連続している ことを確認します。標準偏差(σ)は、周波数安定度 の量的測定です。しかし、統計値では周波数変動の 様子がわかりません。測定ヒストグラムなどのグラ フィック・ツールがあれば、測定変動の特性の詳細が わかります。

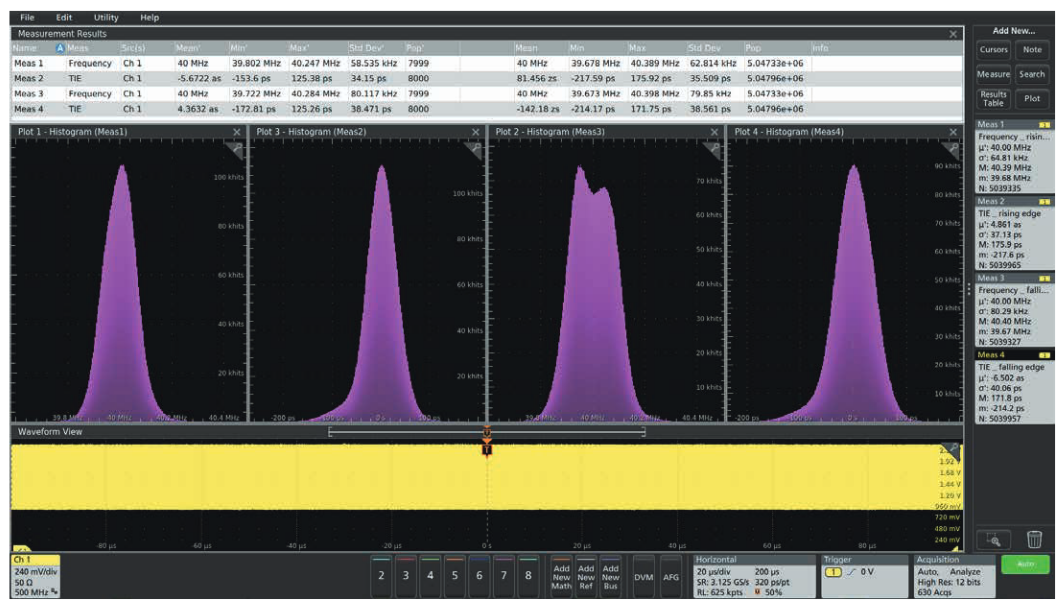

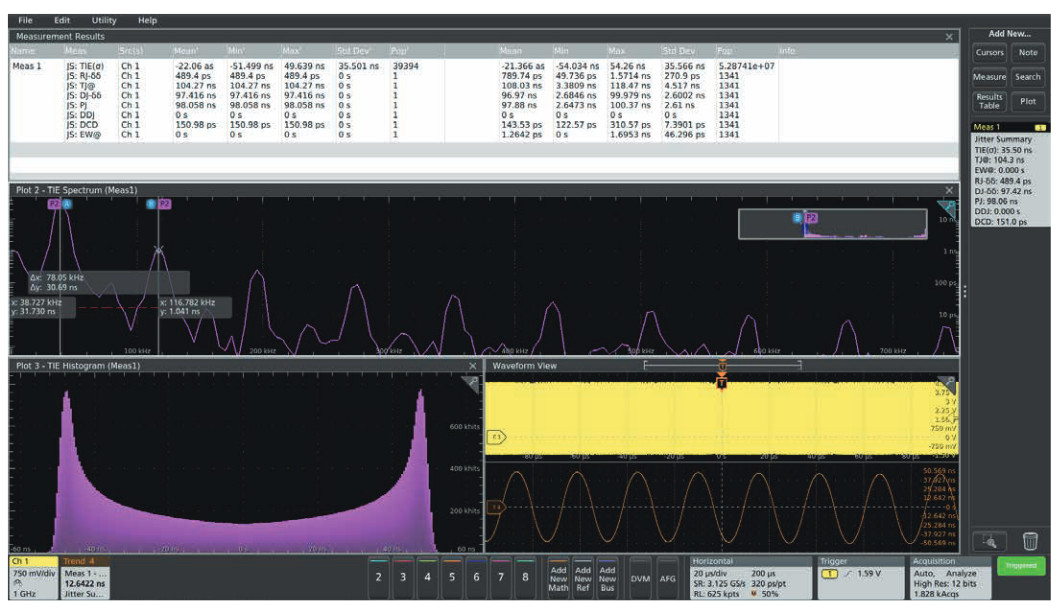

図1の周波数、タイム・インターバル・エラー(TIE)の測定は、40MHzクロック信 号のすべての取込み、すべてのサイクルの立上りと立下りのエッジで測定していま す。このタイミング測定は、取込んだ平均のクロック周波数に対して行われていま す。ディスプレイの右に表示される測定バッジの統計と、ディスプレイ上部に表示 される測定結果の表は、時間と共に変化する測定値の変動の特性評価に役立ちま す。測定結果の表の左側の統計値は現在の取込みのものであり、右側の統計値は すべての取込みの蓄積から得られたものです。

左2つのヒストグラムはクロックの立上りエッジの周波数とTIEの測定のものであり、タイミング変動の理解に役立ちます。この例では、分布は極めてガウシアン特性に近く、ジッタは主にランダム性であることがわかります。

一方、右2つのヒストグラムはクロックの立下りエッジの周波数とTIE測定のものです。周波数測定のヒストグラムの形状は大きく異なっており、より詳細な調査が必要です。

図1に示すすべての解析は、5シリーズMSOの標準機能で行われています。タイミング変動の詳細な解析は、オプションの拡張ジッタ/タイミング測定機能で行うことができます。

拡張ジッタ解析

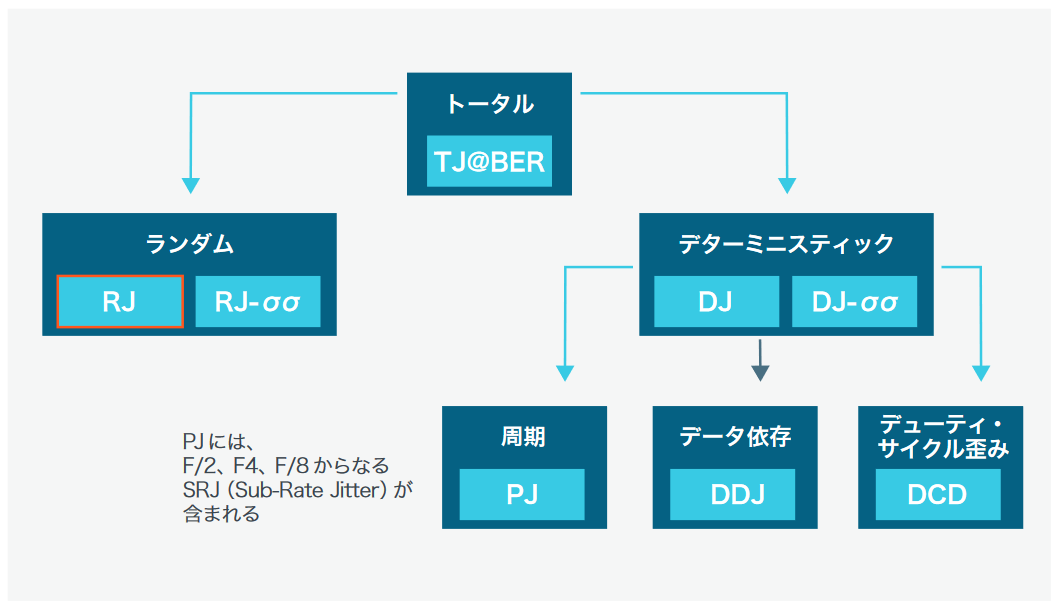

図2に示すように、タイミング・ジッタはいくつかの成分に分離でき、タイミング違反の詳細な根本原因を調べることができます。ここからは、5シリーズMSOの拡張ジッタ測定機能を使用した、ジッタの分離とその結果の解釈に関する、実践的な例を説明します。

40MHz非変調クロックの再考

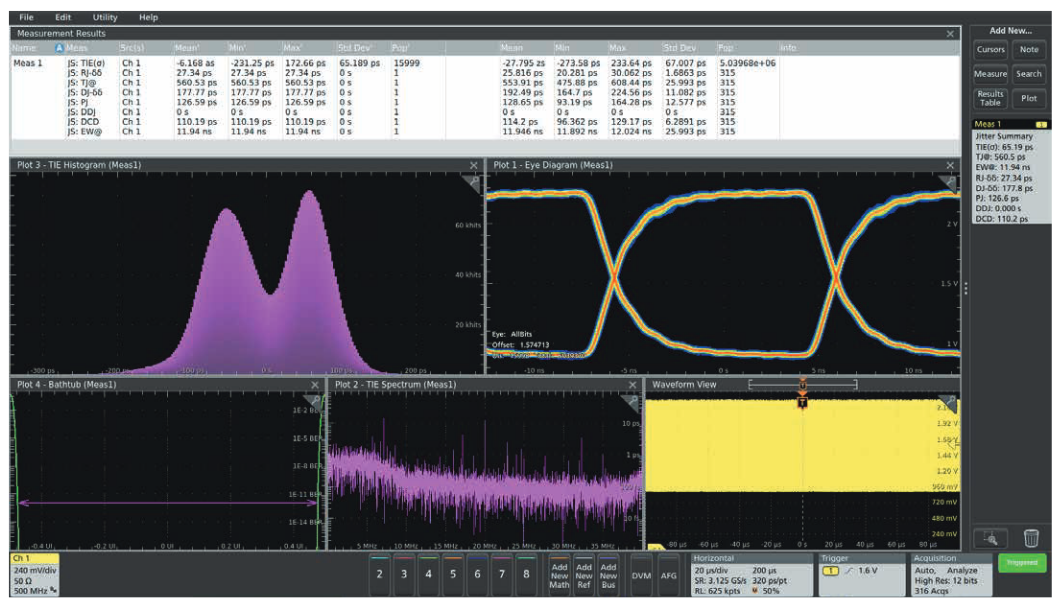

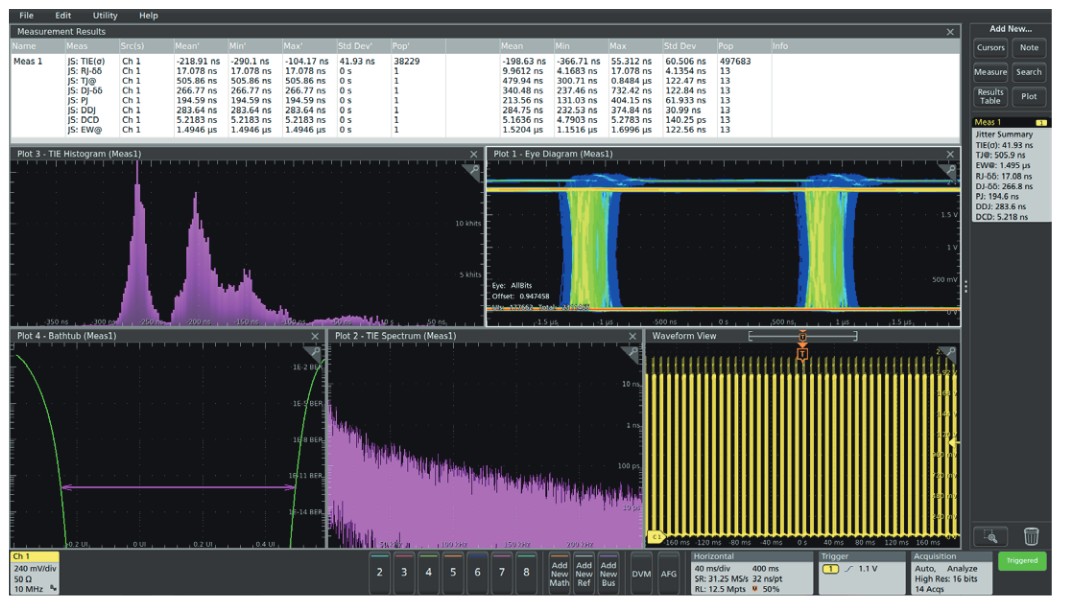

図1の40MHzクロック例に対して5シリーズMSOのオプションである拡張ジッタ測定機能でジッタ・サマリ測定を実行すると、新しい手がかりが示されます。図3のジッタ・サマリ測定では、信号のアイ・ダイアグラム、TIEの測定、TIE測定のヒストグラムとスペクトラム、ジッタの各コンポーネントへの分離が行われています。

一見すると、図3のアイ・ダイアグラムのアイの開口からは、クロック信号のジッタは非常に小さく見えます。トータル・ジッタ(TJ@BER)は約554psであり、40MHzのクロック信号の約2.2%にあたります。ジッタ分離では、ランダム・ジッタ成分(RJ-δδ)はトータル・ジッタの非常に小さな要素となっています。

したがって、デターミニスティック・ジッタ(DJ-δδ)* が支配的な成分になっているはずです。TIEヒストグラムの二峰性からも、強いデターミニスティック・ジッタ成分がうかがえます。DJはさらに、周期ジッタ(PJ)、データ依存性ジッタ(DDJ)、デューティ・サイクル歪み(DCD)に分離されます。

PJはジッタの約1/4です。TIEのプロットを見るとスペ クト ラ ム 成 分 が は っ き り と 表 れ て お り、7、17、 32MHzに強いピークがあり、デターミニスティック・ ジッタとは関係がなく、基板またはFPGAの信号クロ ストークによるものと思われます。これはデータ信号 ではなく、クロック信号のため、DDJはゼロです。 DCDもトータル・ジッタの約1/5であり、クロックの 形状をした回路はさらに詳細な解析と最適化が必要 であることを示しています。

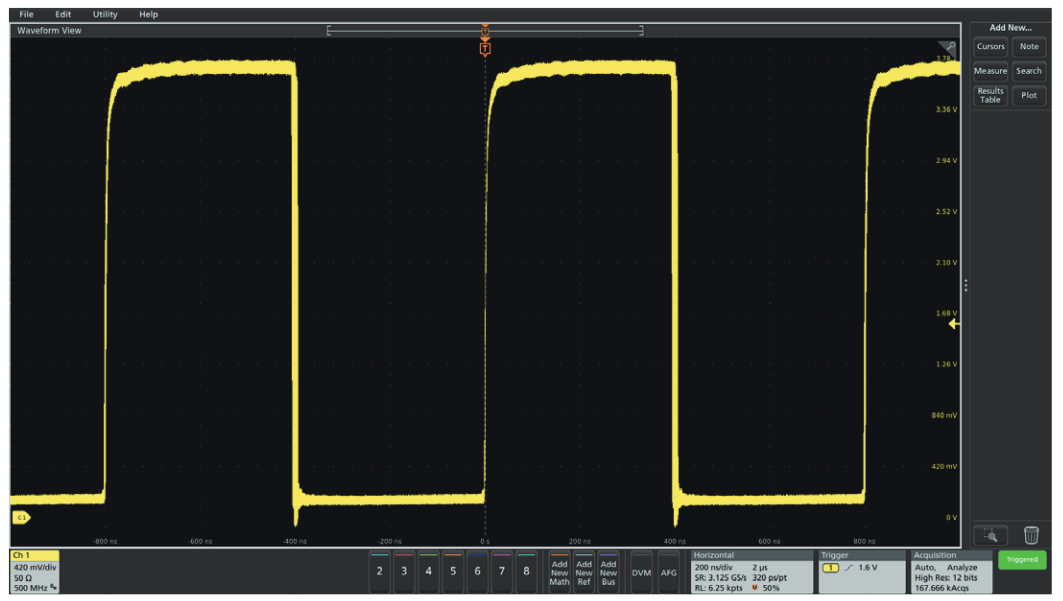

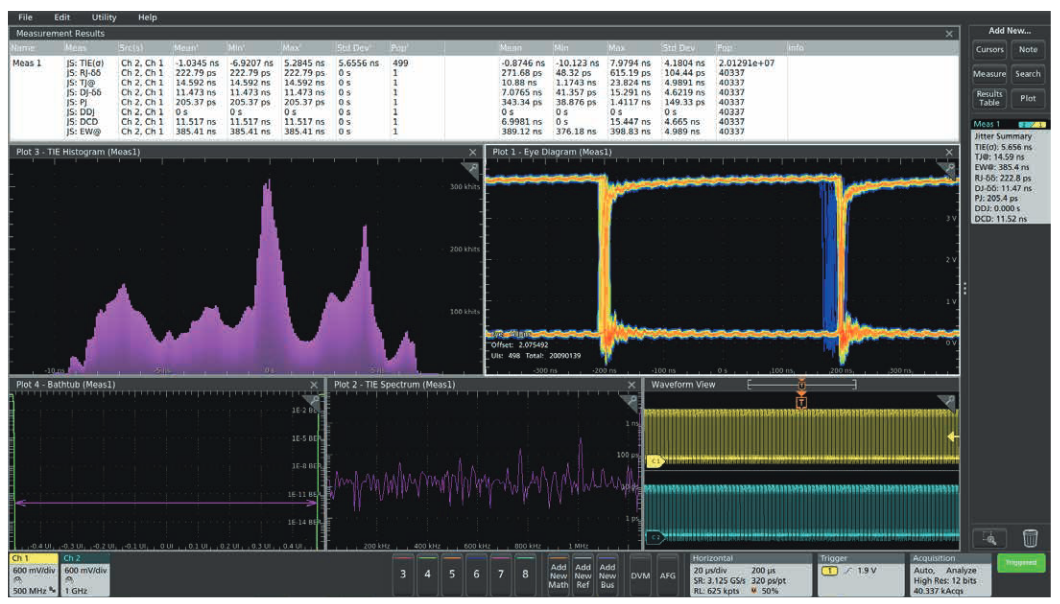

図4は、システム内の別のクロック信号解析を示していますが、異なったジッタ特 性を示しています。アイ・ダイアグラムのアイ開口を見ると、クロック信号のジッ タは小さいと言えます。トータル・ジッタの値が約4.4nsであり、クロック周期の 0.55%未満であることからも検証できます。ジッタ分離では、ランダム・ジッタ成 分はトータル・ジッタの非常に小さな要素となっています。周期ジッタも比較的小 さく、TIEのスペクトラム・プロットからも大きなスペクトラム成分は見当たりま せん。このことから、信号のジッタはデターミニスティック・ジッタの非相関成分 には関係していないことがわかります。また、これはデータ信号ではなく、クロッ ク信号であるため、データ依存性ジッタはゼロです。しかし、デューティ・サイク ル歪みがトータル・ジッタの主な成分になっています。

この手がかりをもとに図5に示すクロック信号のパーシスタンス表示を見ると、信号の立下りエッジでデューティ・サイクルが大きく変動していることがわかります。組込みシステムがクロックの立上りエッジを使用する場合は、このデューティ・サイクルの変動は問題にはなりません。しかし、回路の一部が立上りエッジを使用し、他の部分で立下りエッジを使用する場合、ジッタが原因となってシステムは不正確または不安定な動作になることがあります。

スペクトラム拡散クロックの特性評価

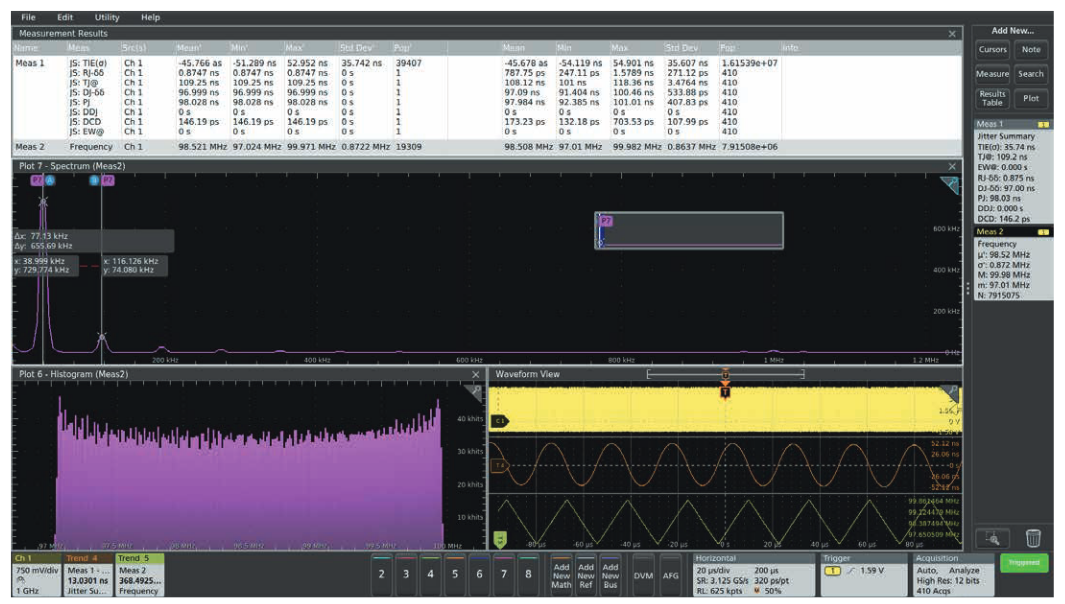

この設計のクロック解析の最後の例を、図6に示します。トリガ・ポイントから水平軸方向に離れるにしたがって波形が不鮮明になっているように、周波数測定は時間とともに約97MHzから約100MHzの間で変化しており、クロック周期も変化しています。

測定の統計値を見ると、周波数の変動を定量化するのに役立ち、クロックの周波数が設計仕様内にあることを確認できますが、周波数が変動する理由を理解するのには役立ちません。この例では、信号はスペクトラム拡散しており、周波数は意図的に変調されています。しかし、期待通りに動作しているのでしょうか。

繰返しになりますが、ジッタ・サマリにはさまざまな情報が表示されます。上に表示される測定結果の表と、サドル形状のTIEヒストグラムから、周波数の変動(ジッタ)はPJが主な原因であることがわかります。

変調で発生するタイム・インターバル・エラー(TIE)は、画面右下に表示されるオレンジ色の時間トレンドが観測できます。TIEのタイム・トレンド波形と、画面中央に表示されるTIEスペクトラム・ピークのカーソル測定から、変調レートは約39kHzとわかります。

奇数の高調波と急速に低下する振幅から、変調波は方形波または三角波波形と思われます。しかし、TIEは実際の変調信号の積分であることから、スペクトラム拡散クロックは39kHzの三角波で変調されていると結論付けることができます。

この理論を検証するため、周波数を測定し、測定ヒストグラム、スペクトラム、タイム・トレンドをプロットします。スペクトラムのカーソル測定から、実際に変調は39kHzの三角波であることがわかります。測定ヒストグラムは97~100MHzで期待通りフラットであり、タイム・トレンドで同じ変調が確認できます。

ロースピード・シリアル・バスのジッタ測定

ジッタは、セルフクロッキング・バスを含むシリアル・バスの性能にも影響します。図9は、500kbps差動CANバス信号のトランスミッタにおけるジッタ・サマリ解析の例を示しています。同じような測定は、他のシリアル・バスのトランスミッタ、レシーバでも行えます。

この解析の最初の手順は、シリアル・データ信号からクロック信号をリカバリすることです。この例では、ソフトウェアは狭いループ帯域のPLL(Phase Locked Loop)でクロックをリカバし、データ・バースト間の同期を保持しています。リカバリされたクロックは、ジッタ解析のタイミング・リファレンスとして使用されます。

ジッタ分離の結果から、トランスミッタにおけるトータル・ジッタの主な成分はDDJ(データ依存性ジッタ)であり、ランダム・ジッタ、デューティ・サイクル依存成分は非常に小さいことがわかります。各データ・バーストの始めの信号における振幅変調に関係すると思われる周期ジッタ成分もあり(個々のデータ・ビットには関係しません)、これはアイ・ダイアグラムとタイムドメイン表示で確認できます。

クロック・データのジッタ測定

ジッタ解析の最後の例は、同期論理回路です。これまでの例と違い、この回路にははっきりしたクロック信号があるため、ジッタ測定はCh. 1の黄色のクロック信号に対するCh. 2の青のデータ信号で行います(図10の右下)。

クロック・レートはちょうど1.25MHzで回路基板の配線は短いため、信号は小さなランダム・ジッタ、開いたアイ・パターンが示すように、信号はとてもきれいな状態です。この回路は個別のクロック信号を使用しているため、ジッタはデータ依存性でないことが期待されます。

この例では、ジッタはデューティ・サイクル歪みが支配的であるように見えます。回路を詳細に解析した結果、この回路のクロックは図5のクロックで得られたものであることがわかりました。この回路のトータル・ジッタの大部分がクロック信号のデューティ・サイクル歪みが原因であることは偶然ではありません。