This content has been recently updated. Please click DOWNLOAD FILE to view the most recent version in PDF format.

C-V Characterization of MOS Capacitors Using the Model 4200-SCS Parameter Analyzer

Introduction

Maintaining the quality and reliability of gate oxides of MOS structures is a critical task in a semiconductor fab. Capacitance-evoltage (C-V) measurements are commonly used in studying gate-oxide quality in detail. These measurements are made on a two-terminal device called a MOS capacitor (MOS cap), which is basically a MOSFET without a source and drain. C-V test results offer a wealth of device and process information, including bulk and interface charges. Many MOS device parameters, such as oxide thickness, flatband voltage, threshold voltage, etc., can also be extracted from the C-V data.

Using a tool such as the Keithley Model 4200-SCS equipped with the 4200-CVU Integrated C-V Option for making C-V measurements on MOS capacitors can simplify testing and analysis. The Model 4200-SCS is an integrated measurement system that can include instruments for both I-V and C-V measurements, as well as software, graphics, and mathematical analysis capabilities. The software incorporates C-V tests, which include a variety of complex formulas for extracting common C-V parameters.

This application note discusses how to use a Keithley Model 4200-SCS Parameter Analyzer equipped with the Model 4200-CVU Integrated C-V Option to make C-V measurements on MOS capacitors. It also addresses the basic principles of MOS caps, performing C-V measurements on MOS capacitors, extracting common C-V parameters, and measurement techniques. The Keithley Test Environment Interactive (KTEI) software that controls the Model 4200-SCS incorporates a list of a dozen test projects specific to C-V testing. Each project is paired with the formulae necessary to extract common C-V parameters, such as oxide capacitance, oxide thickness, doping density, depletion depth, Debye length, flatband capacitance, flatband voltage, bulk potential, threshold voltage, metal-semiconductor work function difference, and effective oxide charge. This completeness is in sharp contrast to other commercially available C-V solutions, which typically require the user to research and enter the correct formula for each parameter manually.

Overview of C-V Measurement Technique

By definition, capacitance is the change in charge (Q) in a device that occurs when it also has a change in voltage (V):

| C ≡ | ∆Q |

| ∆V |

One general practical way to implement this is to apply a small AC voltage signal (millivolt range) to the device under test, and then measure the resulting current. Integrate the current over time to derive Q and then calculate C from Q and V.

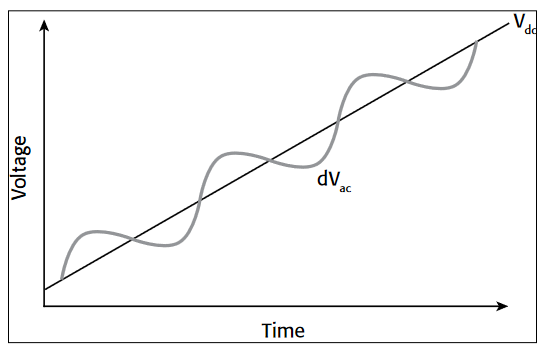

C-V measurements in a semiconductor device are made using two simultaneous voltage sources: an applied AC voltage signal (dVac) and a DC voltage (Vdc) that is swept in time, as illustrated in Figure 1.

The magnitude and frequency of the AC voltage are fixed; the magnitude of the DC voltage is swept in time. The purpose of the DC voltage bias is to allow sampling of the material at different depths in the device. The AC voltage bias provides the small-signal bias so the capacitance measurement can be performed at a given depth in the device.

Basic Principles of MOS Capacitors

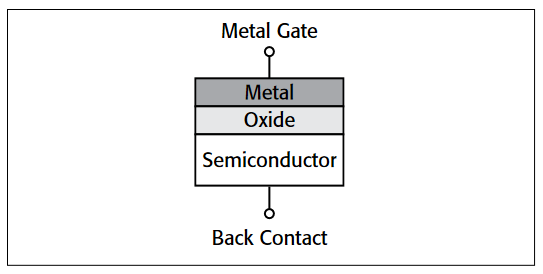

Figure 2 illustrates the construction of a MOS capacitor. Essentially, the MOS capacitor is just an oxide placed between a semiconductor and a metal gate. The semiconductor and the metal gate are the two plates of the capacitor. The oxide functions as the dielectric. The area of the metal gate defines the area of the capacitor.

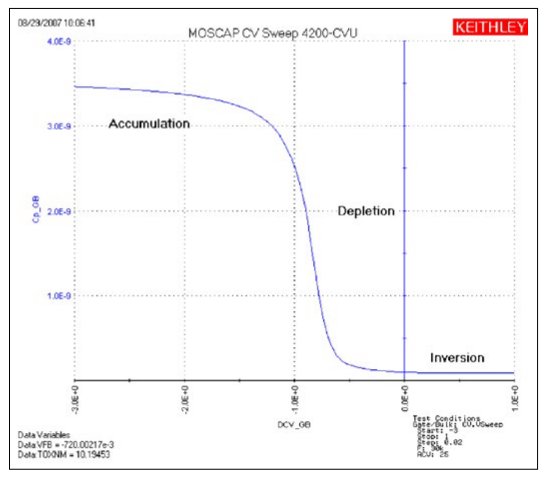

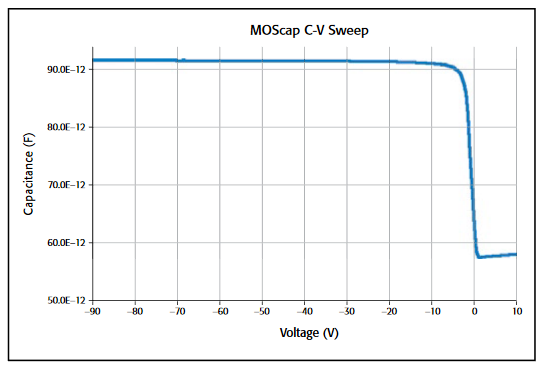

The most important property of the MOS capacitor is that its capacitance changes with an applied DC voltage. As a result, the modes of operation of the MOS capacitor change as a function of the applied voltage. Figure 3 illustrates a high frequency C-V curve for a p-type semiconductor substrate. As a DC sweep voltage is applied to the gate, it causes the device to pass through accumulation, depletion, and inversion regions.

The three modes of operation, accumulation, depletion and inversion, will now be discussed for the case of a p-type semiconductor, then briefly discussed for an n-type semiconductor at the end of this section.

Accumulation Region

With no voltage applied, a p-type semiconductor has holes, or majority carriers, in the valence band. When a negative voltage is applied between the metal gate and the semiconductor, more holes will appear in the valence band at the oxide-semiconductor interface. This is because the negative charge of the metal causes an equal net positive charge to accumulate at the interface between the semiconductor and the oxide. This state of the p-type semiconductor is called accumulation.

For a p-type MOS capacitor, the oxide capacitance is measured in the strong accumulation region. This is where the voltage is negative enough that the capacitance is essentially constant and the C-V curve is almost flat. This is where the oxide thickness can also be extracted from the oxide capacitance.

However, for a very thin oxide, the slope of the C-V curve doesn't flatten in accumulation and the measured oxide capacitance differs from the actual oxide capacitance.

Depletion Region

When a positive voltage is applied between the gate and the semiconductor, the majority carriers are replaced from the semiconductor-oxide interface. This state of the semiconductor is called depletion because the surface of the semiconductor is depleted of majority carriers. This area of the semiconductor acts as a dielectric because it can no longer contain or conduct charge. In effect, it becomes an insulator.

The total measured capacitance now becomes the oxide capacitance and the depletion layer capacitance in series, and as a result, the measured capacitance decreases. This decrease in capacitance is illustrated in Figure 3 in the depletion region. As a gate voltage increases, the depletion region moves away from the gate, increasing the effective thickness of the dielectric between the gate and the substrate, thereby reducing the capacitance.

Inversion Region

As the gate voltage of a p-type MOS-C increases beyond the threshold voltage, dynamic carrier generation and recombination move toward net carrier generation. The positive gate voltage generates electron-hole pairs and attracts electrons (the minority carriers) toward the gate. Again, because the oxide is a good insulator, these minority carriers accumulate at the substrate-to-oxide/well-to-oxide interface. The accumulated minority-carrier layer is called the inversion layer because the carrier polarity is inverted. Above a certain positive gate voltage, most available minority carriers are in the inversion layer, and further gate voltage increases do not further deplete the semiconductor. That is, the depletion region reaches a maximum depth.

Once the depletion region reaches a maximum depth, the capacitance that is measured by the high frequency capacitance meter is the oxide capacitance in series with the maximum depletion capacitance. This capacitance is often referred to as minimum capacitance. The C-V curve slope is almost flat.

NOTE: The measured inversion-region capacitance at the maximum depletion depth depends on the measurement frequency. Therefore, C-V curves measured at different frequencies may have different appearances. Generally, such differences are more significant at lower frequencies and less significant at higher frequencies.

n-type Substrate

The C-V curve for an n-type MOS capacitor is analogous to a p-type curve, except that (1) the majority carriers are electrons instead of holes; (2) the n-type C-V curve is essentially a mirror image of the p-type curve; (3) accumulation occurs by applying a positive voltage to the gate; and (4) the inversion region occurs at negative voltage.

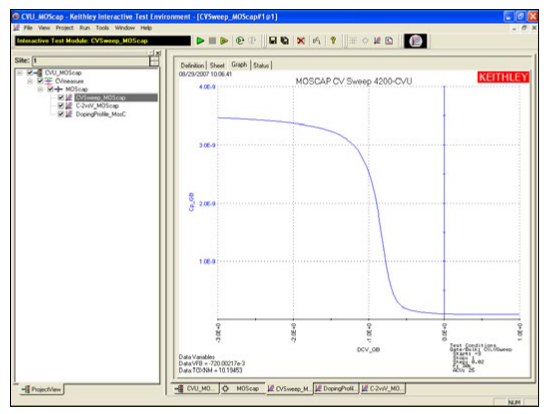

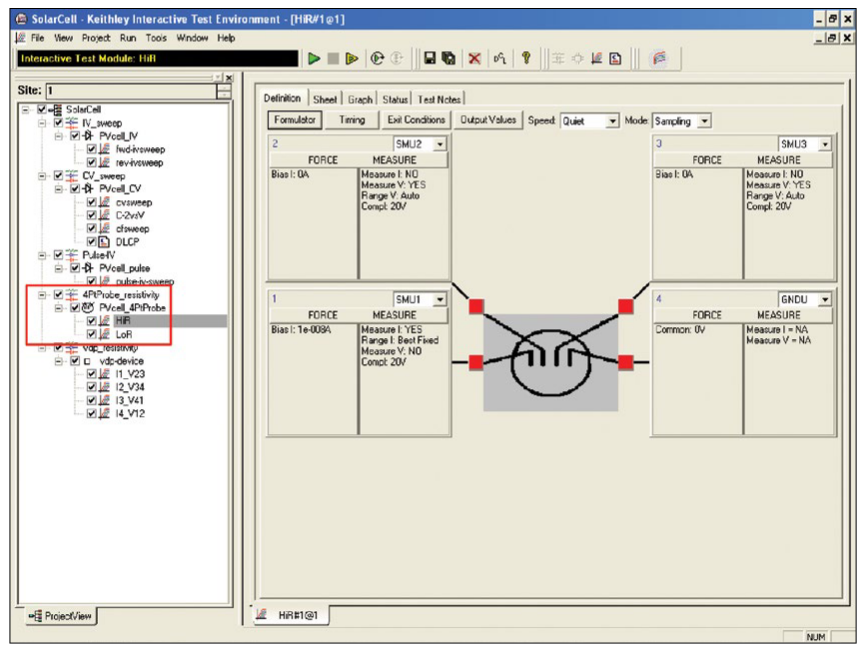

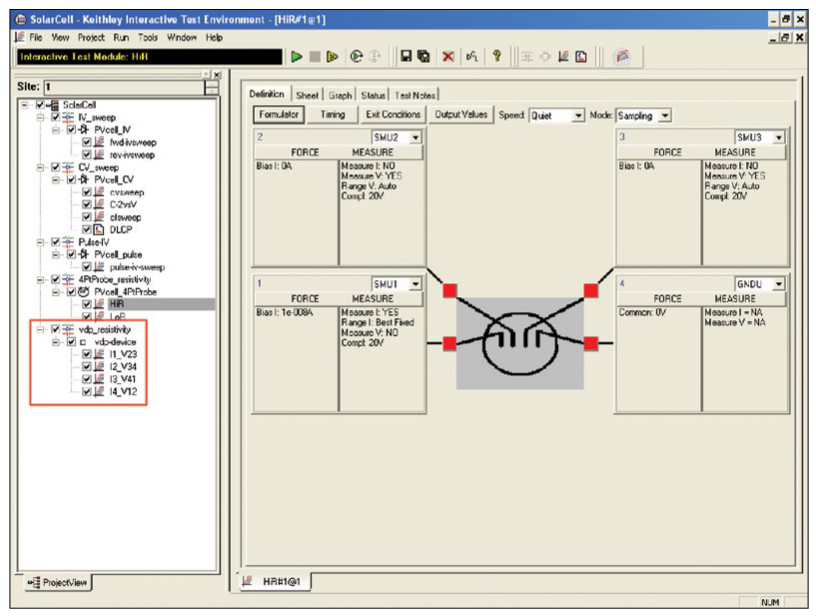

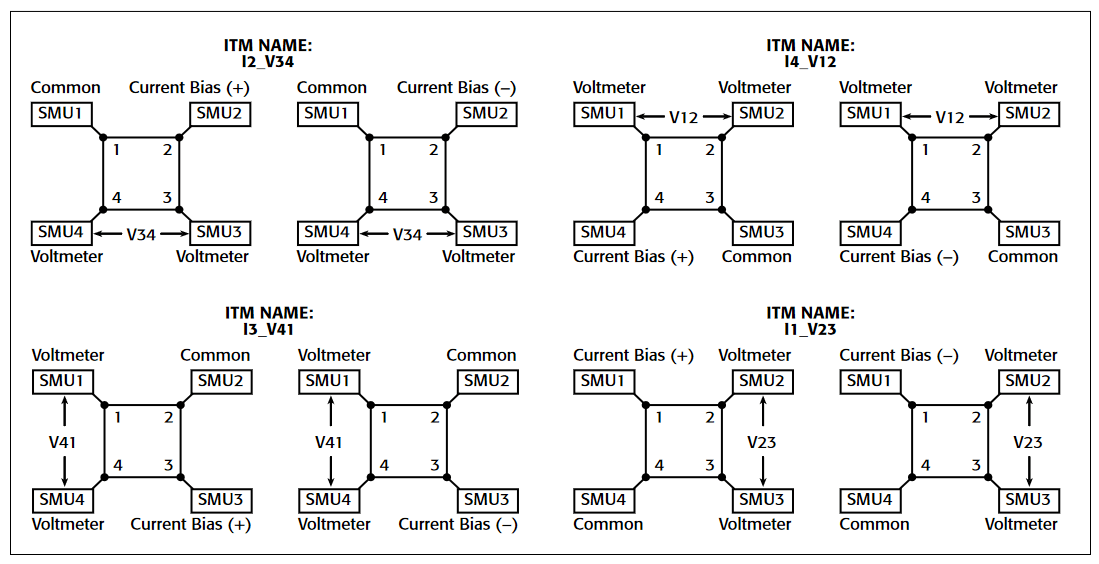

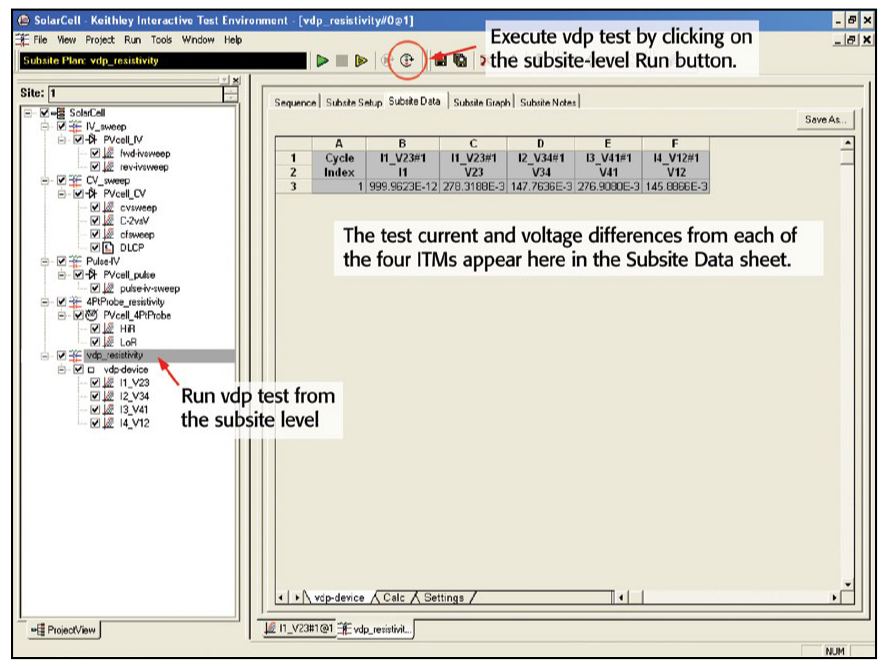

Performing C-V Measurements with the 4200-CVU

To simplify testing, a project has been created for the 4200-SCS that makes C-V measurements on a MOS capacitor and extracts common measurement parameters such as oxide thickness, flatband voltage, threshold voltage, etc. The project (CVU_MOScap) is included with all 4200-SCS systems running KTEI Version 7.0 or later. Figure 4 is a screen shot of the project, which has three tests, called ITMs (Interactive Test Modules), which generate a C-V sweep (CVSweep_MOScap), a 1/C2 vs.Gate Voltage curve (C-2vsV_MOScap), and a doping profile (DopingProfile_MosC). Figure 4 also illustrates a C-V sweep generated with the (CVSweep_MOScap) test module. All of the extracted C-V parameters in these test modules are defined in the next section of this application note.

CVSweep_MOScap Test Module

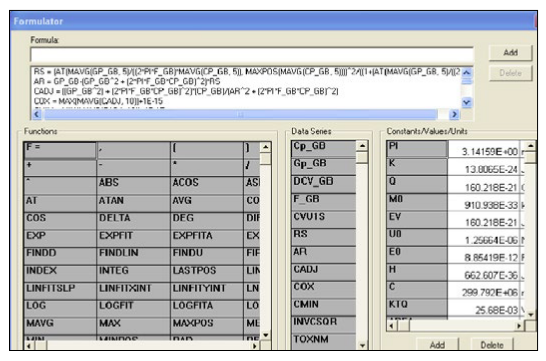

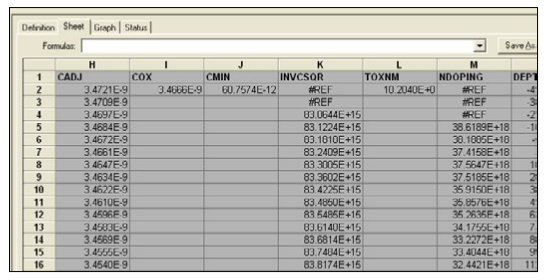

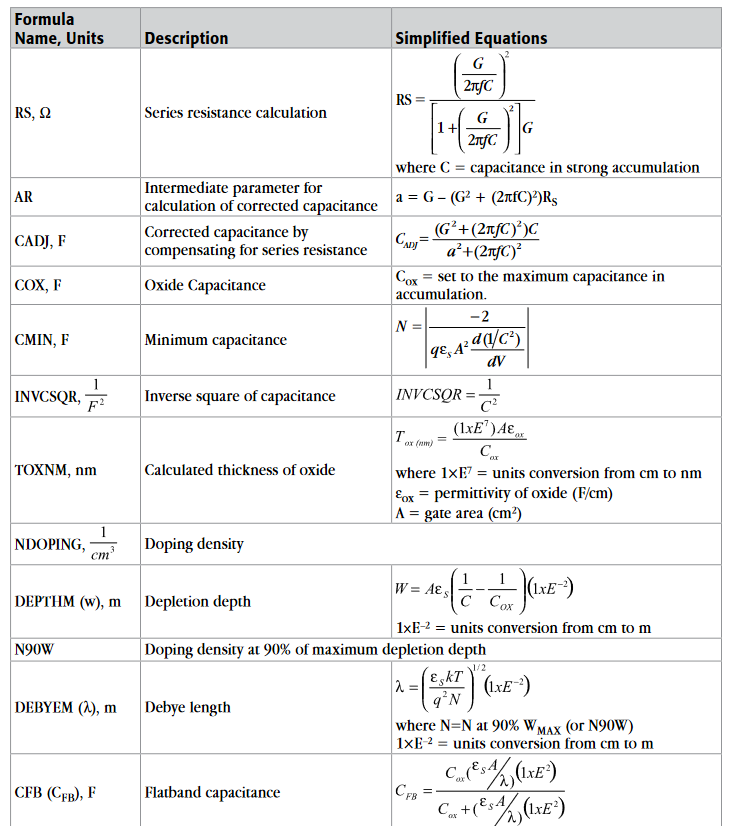

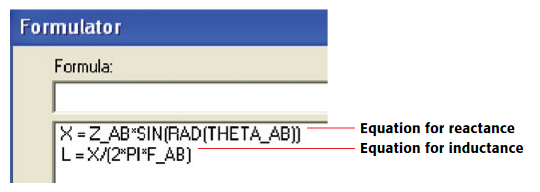

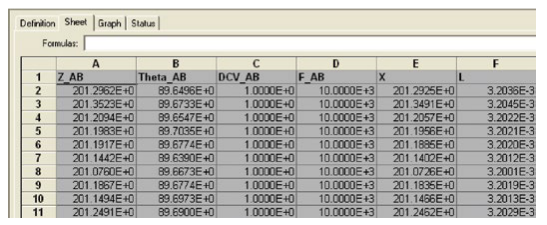

This test performs a capacitance measurement at each step of a user-configured linear voltage sweep. A C-V graph is generated from the acquired data, and several device parameters are calculated using the Formulator, which is a tool in the 4200-SCS's software that provides a variety of computational functions, common mathematical operators, and common constants. Figure 5 shows the window of the Formulator. These derived parameters are listed in the Sheet Tab of the Test Module.

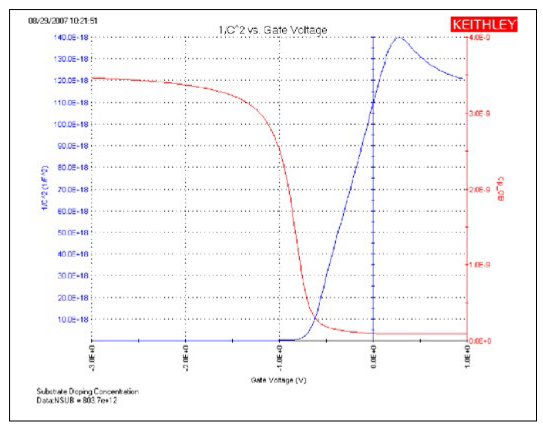

C-2vsV_MOScap Test Module

This test performs a C-V sweep and displays the capacitance (1/C2) as a function of the gate voltage (VG). This sweep can yield important information about doping profile because the substrate doping concentration (NSUB) is inversely related to the reciprocal of the slope of the 1/C2 vs. VG curve. A positive slope indicates acceptors and a negative slope indicates donors. The substrate doping concentration is extracted from the slope of the 1/C2 curve and is displayed on the graph. Figure 6 shows the results of executing this test module.

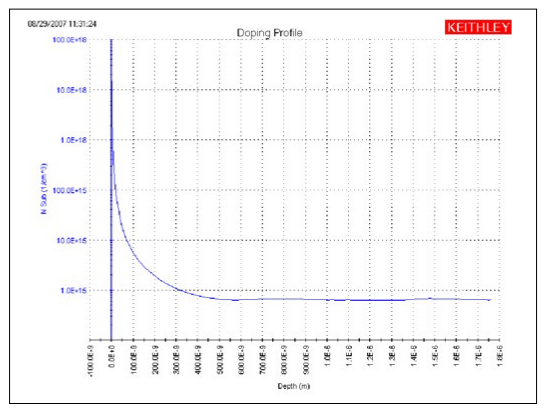

Doping Profile Test Module

This test performs a doping profile, which is a plot of the doping concentration vs. depletion depth. The difference in capacitance at each step of the gate voltage is proportional to the doping concentration. The depletion depth is computed from the high frequency capacitance and oxide capacitance at each measured value of the gate voltage. The results are plotted on the graph as shown in Figure 7.

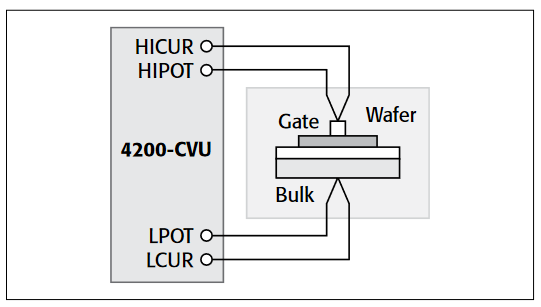

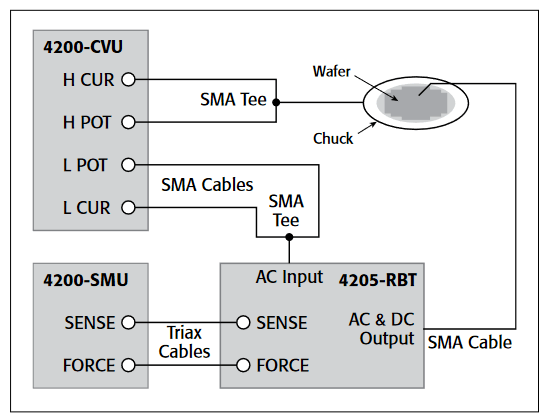

Connections to the 4200-CVU

To make a C-V measurement, a MOS cap is connected to the 4200-CVU as shown in Figure 8. In the ITM, both the 4200-CVU ammeter and the DC voltage appear at the HCUR/HPOT terminals. See the next section, "Measurement Optimization," for further information on connecting the CVU to the device on a wafer.

Measurement Optimization

Successful measurements require compensating for stray capacitance, measuring at equilibrium conditions, and compensating for series resistance.

Offset Correction for Stray Capacitance

C-V measurements on a MOS capacitor are typically performed on a wafer using a prober. The 4200-CVU is designed to be connected to the prober via interconnect cables and adaptors and may possibly be routed through a switch matrix. This cabling and switch matrix will add stray capacitance to the measurements.

To correct for stray capacitance, the KTEI software environment has a built-in tool for offset correction, which is a two-part process: the corrections for OPEN and/or SHORT are performed first, and then they can be enabled within an ITM. To perform the corrections, Open the Tools Menu and select CVU Connection Compensation. For an Open correction, click on Measure Open. Probes must be up during the correction. Open is typically used for high impedance measurements (<10pF or >1MΩ).

For a Short correction, click on Measure Short. Short the probe to the chuck. A short correction is generally performed for low impedance measurements (>10nF or <10Ω).

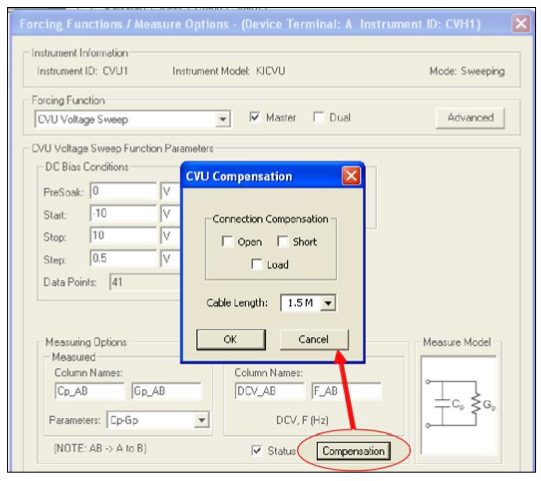

After the corrections are performed, they must be enabled in the project. To enable corrections, click the Compensation button at the bottom of the Forcing Functions/Measure Options Window. In the CVU Compensation dialog box (Figure 9), click only the corrections to be applied.

Measuring at Equilibrium Conditions

A MOS capacitor takes time to become fully charged after a voltage step is applied. C-V measurement data should only be recorded after the device is fully charged. This condition is called the equilibrium condition. Therefore, to allow the MOS capacitor to reach equilibrium: (1) allow a sufficient Hold Time in the Timing Menu to enable the MOS capacitor to charge up while applying a "PreSoak" voltage, and (2) allow a sufficient Sweep Delay Time in the Timing Menu before recording the capacitance after each voltage step of a voltage sweep. The appropriate Hold and Delay Times are determined experimentally by generating capacitance vs. time plots and observing the time for the capacitance to settle.

Although C-V curves swept from different directions may look different, allowing adequate Hold and Delay Times minimizes such differences. One way to determine sufficient Hold and Delay Times is to generate a series of C-V curves in both directions. Change the Hold and Delay Times for each pair of inversion ➞ accumulation and accumulation ➞ inversion curves until the curves look essentially the same for both sweep directions.

Hold and Delay Times When Sweeping from Inversion ➞ Accumulation. When the C-V sweep starts in the inversion region and the starting voltage is initially applied, a MOS capacitor is driven into deep depletion. Thereafter, if the starting voltage is maintained, the initial high frequency C-V curve climbs toward and ultimately stabilizes to the minimum capacitance at equilibrium. However, if the initial Hold Time is too short, the MOS capacitor cannot adequately recover from deep depletion, and the measured capacitance will be smaller than the minimum capacitance at equilibrium. Set the "PreSoak" voltage to the first voltage in the voltage sweep and allow a sufficient Hold Time for the MOS capacitor to reach equilibrium.

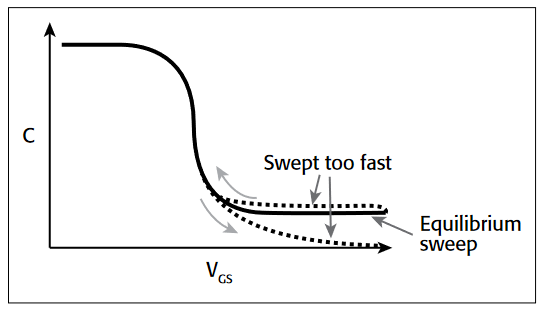

However, once the MOS capacitor has reached equilibrium after applying the "PreSoak" voltage, an inversion ➞ accumulation C-V sweep may be performed with small delay times. This is possible because minority carriers recombine relatively quickly as the gate voltage is reduced. Nonetheless, if the Delay Time is too short, non-equilibrium occurs, and the capacitance in the inversion region is slightly higher than the equilibrium value. This is illustrated by the upper dotted line in Figure 10.

Hold and Delay Times When Sweeping from Accumulation ➞ Inversion. When the C-V sweep starts in the accumulation region, the effects of Hold and Delay Times in the accumulation and depletion regions are fairly subtle. However, in the inversion region, if the Delay Time is too small (i.e., the sweep time is too fast), there's not enough time for the MOS capacitor to generate minority carriers to form an inversion layer. On the high frequency C-V curve, the MOS capacitor never achieves equilibrium and eventually becomes deeply depleted. The measured capacitance values fall well below the equilibrium minimum value. The lower dotted line in Figure 10 illustrates this phenomenon.

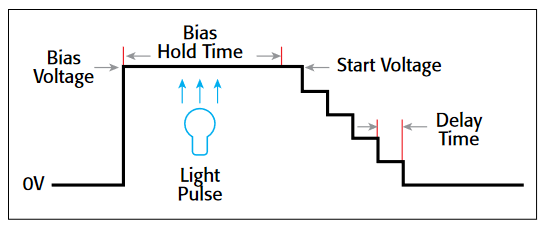

Using the preferred sequence. Generating a C-V curve by sweeping from inversion to accumulation is faster and more controllable than sweeping from accumulation to inversion. Figure 11 illustrates a preferred measurement sequence.

The device is first biased at the "PreSoak" voltage for the Hold Time that is adjusted in the Timing Menu. The bias or "PreSoak" voltage should be the same as the sweep start voltage to avoid a sudden voltage change when the sweep starts. During biasing, if necessary, a short light pulse can be applied to the sample to help generate minority carriers. However, before the sweep starts, all lights should be turned off. All measurements should be performed in total darkness because the semiconductor material may be light sensitive. During the sweep, the Delay Time should be chosen to create the optimal balance between measurement speed and measurement integrity, which requires adequate equilibration time.

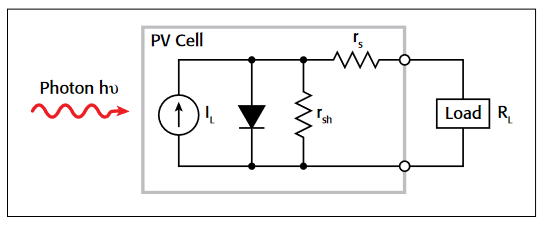

Compensating for series resistance

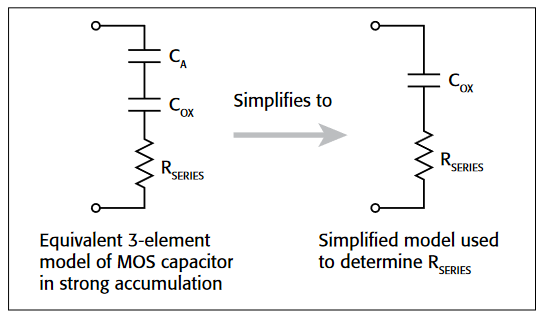

After generating a C-V curve, it may be necessary to compensate for series resistance in measurements. The series resistance (RSERIES) can be attributed to either the substrate (well) or the backside of the wafer. For wafers typically produced in fabs, the substrate bulk resistance is fairly small (<10Ω) and has negligible impact on C-V measurements. However, if the backside of the wafer is used as an electrical contact, the series resistance due to oxides can significantly distort a measured C-V curve. Without series compensation, the measured capacitance can be lower than the expected capacitance, and C-V curves can be distorted. Tests for this project compensate for series resistance using the simplified three-element model shown in Figure 12. In this model, COX is the oxide capacitance and CA is the capacitance of the accumulation layer. The series resistance is represented by RSERIES.

The corrected capacitance (CADJ) and corrected conductance (GADJ) are calculated from the following formulas [1]:

| CADJ = | (G2 + (2πƒ∁)2)∁ |

| a2R + (2πƒ∁)2 |

| GADJ = | (G2 + (2πƒ∁)2)aR |

| a2R + (2πƒ∁)2 |

where:

| aR = | G - (G2 + (2πƒ∁)2)Rs |

CADJ = series resistance compensated parallel model capacitance

C = measured parallel model capacitance

GADJ = series resistance compensated conductance

G = measured conductance

f = test frequency as set in the KITE Definition Tab

RS = series resistance

The series resistance (RS) may be calculated from the capacitance and conductance values that are measured while biasing the DUT (device under test) in the accumulation region as follows:

| RS = | (G2 + (2πƒ∁)2)aR |

| a2R + (2πƒ∁)2 |

where:

RS = series resistance

G = measured conductance

C = measured parallel model capacitance (in strong accumulation)

ƒ = test frequency as set in KITE (Definition tab)

NOTE: The preceding equations for compensating for series resistance require that the Model 4200-CVU be using the parallel model (Cp-Gp).

For this project, these formulas have been added into the KITE Formulator so the capacitance and conductance can be automatically compensated for the series resistance.

Extracting MOS Device Parameters From C-V Measurements

This section describes the device parameters that are extracted from the C-V data taken in the three test modules in the CVU_MOScap project. The parameters are derived in the Formulator and the calculated values appear in the Sheet tab of each test module as shown in Figure 13.

Oxide thickness

For a relatively thick oxide (>50Å), extracting the oxide thickness is fairly simple. The oxide capacitance (COX) is the high frequency capacitance when the device is biased for strong accumulation. In the strong accumulation region, the MOS-C acts like a parallel-plate capacitor, and the oxide thickness (TOX) may be calculated from COX and the gate area using the following equation:

| TOX(nm) = | (107)Aeox |

| Cox |

where:

TOX = oxide thickness (nm)

A = gate area (cm2)

eOX = permittivity of the oxide material (F/cm)

COX = oxide capacitance (F)

107 = units conversion from cm to nm

Flatband capacitance and flatband voltage

Application of a certain gate voltage, the flatband voltage (VFB), results in the disappearance of band bending. At this point, known as the flatband condition, the semiconductor band is said to become flat. Because the band is flat, the surface potential is zero (with the reference potential being taken as the bulk potential deep in the semiconductor). Flatband voltage and its shift are widely used to extract other device parameters, such as oxide charges.

VFB can be identified from the C-V curve. One way is to use the flatband capacitance method. For this method, the ideal value of the flatband capacitance (CFB) is calculated from the oxide capacitance and the Debye length. The concept of Debye length is introduced later in this section. Once the value of CFB is known, the value of VFB can be obtained from the C-V curve data, by interpolating between the closest gate-to-substrate (VGS) values [2].

The Debye length parameter (λ) must also be calculated to derive the flatband voltage and capacitance. Based on the doping profile, the λ calculation requires one of the following doping concentrations: N at 90% of WMAX (refer to Nicollian and Brews), a user-supplied NA (bulk doping concentration for a p-type, acceptor, material), or a user-supplied ND (bulk doping concentration for an n-type, donor, material).

NOTE: The flatband capacitance method is invalid when the interface trap density (DIT) becomes very large (1012–1013 or greater). However, the method should give satisfactory results for most users. When dealing with high DIT values, consult the appropriate literature for a more suitable method.

The flatband capacitance is calculated as follows:

| CFB = | Cox (εSA/λ) (102) |

| Cox + (εSA/λ) (102) |

where:

CFB = flatband capacitance (F)

COX = oxide capacitance (F)

εS = permittivity of the substrate material (F/cm)

A = gate area (cm2)

102 = units conversion from m to cm

λ = extrinsic Debye length, which is calculated as follows:

| λ = | ( | εSkT | )1/2 | (10-2) |

| q2N |

where:

λ = extrinsic Debye length

εS = permittivity of the substrate material (F/cm)

kT = thermal energy at room temperature (293K) (4.046 × 10-21J)

q = electron charge (1.60219 × 10-19C)

NX = N at 90% WMAX or N90W (refer to Nicollian and Brews; see References) or, when input by the user, NX = NA or NX = ND

10-2 = units conversion from cm to m

The extrinsic Debye length is an idea borrowed from plasma physics. In semiconductors, majority carriers can move freely. The motion is similar to a plasma. Any electrical interaction has a limited range. The Debye length is used to represent this interaction range. Essentially, the Debye length indicates how far an electrical event can be sensed within a semiconductor.

Threshold voltage

The turn-on region for a MOSFET corresponds to the inversion region on its C-V plot. When a MOSFET is turned on, the channel formed corresponds to strong generation of inversion charges. It is these inversion charges that conduct current. When a source and drain are added to a MOS-C to form a MOSFET, a p-type MOS-C becomes an n-type MOSFET, also called an n-channel MOSFET. Conversely, an n-type MOS-C becomes a p-channel MOSFET.

The threshold voltage (VTH) is the point on the C-V curve where the surface potential (φS) equals twice the bulk potential (φB). This curve point corresponds to the onset of strong inversion. For an enhancement-mode MOSFET, VTH corresponds to the point where the device begins to conduct. The physical meaning of the threshold voltage is the same for both a MOS-C C-V curve and a MOSFET I-V curve. However, in practice, the numeric VTH value for a MOSFET may be slightly different due to the particular method used to extract the threshold voltage.

The threshold voltage of a MOS capacitor can be calculated as follows:

| VTH = | VFB ± | [ | A | √4εSq|NBULKφB|+2|φB| ] |

| Cox |

where:

VTH = threshold voltage (V)

VFB = flatband potential (V)

A = gate area (cm2)

COX = oxide capacitance (F)

εS = permittivity of the substrate material (F/cm)

q = electron charge (1.60219 × 10-19C)

NBULK = bulk doping (cm-3) (Note: The Formulator name for NBULK is N90W.)

φB = bulk potential (V) (Note: The Formulator name for φB is PHIB.)

The bulk potential is calculated as follows:

| φB = | - | kT | ln( | NBULK | ) | (DopeType) |

| q | Ni |

where:

φB = bulk potential (V) (Note: The Formulator name for φB is PHIB.)

k = Boltzmann's constant (1.3807 × 10-23J/K)

T = test temperature (K)

q = electron charge (1.60219 × 10-19C)

NBULK = Bulk doping (cm-3) (Note: The Formulator name for NBULK is called N90W.)

Ni = Intrinsic carrier concentration (1.45 × 1010cm-3)

DopeType = +1 for p-type materials and –1 for n-type materials

Metal-semiconductor work function difference

The metal-semiconductor work function difference (WMS) is commonly referred to as the work function. It contributes to the shift in VFB from the ideal zero value, along with the effective oxide charge [3][4]. The work function represents the difference in work necessary to remove an electron from the gate and from the substrate. The work function is derived as follows:

| WMS = | WM - [ WS + | EBG | - φB ] |

| 2 |

where:

WMS = work function

WM = metal work function (V)*

WS = substrate material work function, electron affinity (V)*

EBG = substrate material bandgap (V)*

φB = bulk potential (V) (Note: The Formulator name for φB is PHIB)

*The values for WM, WS, and EBG are listed in the Formulator as constants. The user can change the values depending on the type of materials.

The following example calculates the work function for silicon, silicon dioxide, and aluminum:

| WMS = | 4.1 - [ 4.15 + | 1.12 | - φB ] |

| 2 |

Therefore,

WMS = -0.61 + φB

and

| WMS = | -0.61- | kT | ln( | NBULK | ) | (DopeType) |

| q | Ni |

where:

WMS = work function

k = Boltzmann's constant (1.3807 × 10-23J/K)

T = test temperature (K)

q = electron charge (1.60219 × 10-19C)

NBULK = bulk doping (cm-3)

DopeType = +1 for p-type materials and –1 for n-type materials

For example, for an MOS capacitor with an aluminum gate and p-type silicon (NBULK = 1016cm-3), WMS = -0.95V. Also, for the same gate and n-type silicon (NBULK = 1016cm-3), WMS = -0.27V. Because the supply voltages of modern CMOS devices are lower than those of earlier devices and because aluminum reacts with silicon dioxide, heavily doped polysilicon is often used as the gate material. The goal is to achieve a minimal work-function difference between the gate and the semiconductor, while maintaining the conductive properties of the gate.

Effective and total bulk oxide charge

The effective oxide charge (QEFF) represents the sum of oxide fixed charge (QF), mobile ionic charge (QM), and oxide trapped charge (QOT):

QEFF = QF + QM + QOT

QEFF is distinguished from interface trapped charge (QIT), in that QIT varies with gate bias and QEFF does not [5] [6].Simple measurements of oxide charge using C-V measurements do not distinguish the three components of QEFF. These three components can be distinguished from one another by temperature cycling [7]. Also, because the charge profile in the oxide is not known, the quantity (QEFF) should be used as a relative, not an absolute, measure of charge. It assumes that the charge is located in a sheet at the silicon–silicon dioxide interface.

From Nicollian and Brews, Eq. 10.10, we have:

| VFB - WMS = | - | QEFF |

| Cox |

where:

VFB = flatband potential (V)

WMS = metal-semiconductor work function (V)

QEFF = effective oxide charge (C)

COX = oxide capacitance (F)

Note that COX here is per unit of area. So that:

| QEFF = | COX(WMS - VFB) |

| A |

where:

QEFF = effective oxide charge (C)

COX = oxide capacitance (F)

WMS = metal–semiconductor work function (V)

VFB = flatband potential (V)

A = gate area (cm2)

For example, assume a 0.01cm2, 50pF, p-type MOS-C with a flatband voltage of -5.95V; its NBULK of 1016cm-3 corresponds to a WMS of –0.95 V. For this example, QEFF can be calculated to be 2.5 × 10-8C/cm2, which in turn causes the threshold voltage to shift ~5V in the negative direction. Note that in most cases where the bulk charges are positive, there is a shift toward negative gate voltages. The effective oxide charge concentration (NEFF) is computed from effective oxide charge (QEFF) and the electron charge as follows:

| NEFF = | QEFF |

| q |

where:

NEFF = effective oxide charge density (cm-2)

QEFF = effective oxide charge (C)

q = electron charge (1.60219 × 10-19C)

Substrate doping concentration

The substrate doping concentration (N) is related to the reciprocal of the slope of the 1/C2 vs. VG curve. The doping concentration is calculated and displayed below the graph in the C-2vsV_MOScap test as follows:

| NSUB = | 2 |

| qεsA2(∆1/C2/∆VG) |

where:

NSUB = substrate doping concentration

q = electron charge (1.60219 × 10-19C)

A = gate area (cm2)

εS = permittivity of the substrate material (F/cm)

VG = gate voltage (V)

C = measured capacitance (F)

Doping concentration vs. depth (doping profile)

The doping profile of the device is derived from the C-V curve based on the definition of the differential capacitance as the differential change in depletion region charges produced by a differential change in gate voltage [8].

The standard doping concentration (N) vs. depth (w) analysis discussed here does not compensate for the onset of accumulation, and it is accurate only in depletion. This method becomes inaccurate when the depth is less than two Debye lengths. The doping concentration used in the doping profile is calculated as:

| N = | -2 |

| qεsA2(d(1/C2)/dV) |

The CVU_MOScap project computes the depletion depth (w) from the high frequency capacitance and oxide capacitance at each measured value of the gate voltage (VG) [9]. The Formulator computes each (w) element of the calculated data array as shown:

| W = | Aεs( | 1 | - | 1 | ) | (102) |

| C | COX |

where:

W = depth (m)

A = the gate area (cm2)

C = the measured capacitance (F)

εS = the permittivity of the substrate material (F/cm)

COX = the oxide capacitance (F)

102 = units conversion from cm to m

Once the doping concentration and depletion depth are derived, a doping profile can be plotted. This is done in the Graph tab of the DopingProfile test in the CVU_MOScap project.

Summary

When equipped with the 4200-CVU option, the Model 4200-SCS is a very useful tool for making both C-V and I-V measurements on MOS capacitors and deriving many of the common MOS parameters. In addition to the CVU_MOScap project, the Model 4200-SCS includes other projects specifically for testing MOS capacitors. The CVU_lifetime project is used for determining generation velocity and lifetime testing (Zerbst plot) of MOS capacitors. The CVU_MobileIon project determines the mobile charge of a MOS cap using the bias-temperature stress method.

In addition to making C-V measurements, the SMUs can make I-V measurements on MOS caps, including leakage current and breakdown testing.

Performing Very Low Frequency Capacitance-Voltage Measurements on High Impedance Devices Using the Model 4200-SCS Parameter Analyzer

Introduction

Capacitance measurements on semiconductor devices are usually made using an AC technique with a bridge-type instrument. These AC instruments typically make capacitance and impedance measurements at frequencies ranging from megahertz down to possibly tens of hertz. However, even lower frequency capacitance measurements are often necessary to derive specific test parameters of devices such as MOScaps, thin film transistors (TFTs), and MEMS structures. Low frequency C-V measurements are also used to characterize the slow trapping and de-trapping phenomenon in some materials. Instruments capable of making quasistatic (or almost DC) C-V measurements are often used for these low frequency impedance applications. However, the Model 4200-SCS Parameter Analyzer uses a new narrow-band technique that takes advantage of the low current measurement capability of its integrated source measure unit (SMU) instruments to perform C-V measurements at specified low frequencies in the range of 10mHz to 10Hz. This new method is called the Very Low Frequency C-V (VLF C-V) Technique.

The VLF C-V Technique makes it possible to measure very small capacitances at a precise low test frequency. This patent pending, narrow-band sinusoidal technique allows for low frequency C-V measurements of very high impedance devices, up to >1E15 ohms. Other AC impedance instruments are usually limited to impedances up to about 1E6 to 1E9 ohms. The VLF C-V approach also reduces the noise that may occur when making traditional quasistatic C-V measurements.

The Model 4200-SCS Parameter Analyzer comes with preconfigured tests and a user library to perform impedance measurements automatically using this very low frequency technique. Because this approach uses the Model 4200-SCS's SMU instruments, no additional hardware or software is necessary if low current I-V characterization is already required. This application note describes the VLF C-V technique, explains how to make connections to the DUT, shows how to use the provided software, and describes optimizing VLF C-V measurements using the Model 4200-SCS.

Very Low Frequency C-V Technique

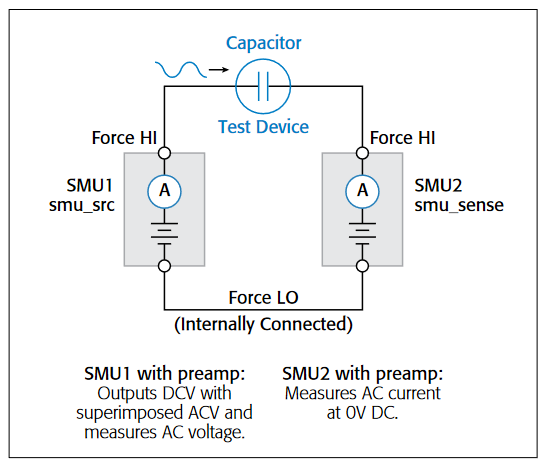

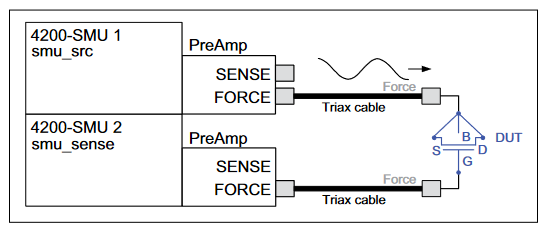

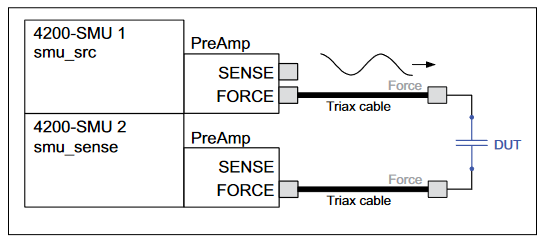

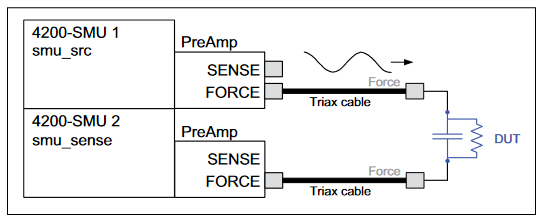

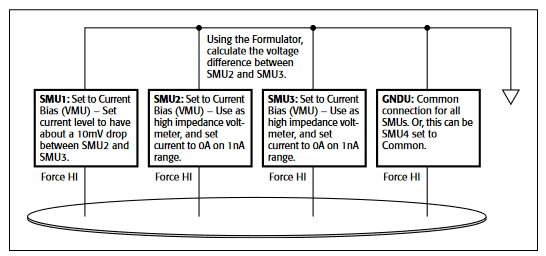

Figure 1 is a simplified diagram of the SMU instrument configuration used to generate the low frequency impedance measurements. This configuration requires a Model 4200-SCS system with two SMU instruments installed, with Model 4200-PA preamps connected to either side of the device under test. SMU1 outputs the DC bias with a superimposed AC signal and also measures the voltage. SMU2 measures the resulting AC current while sourcing 0V DC.

Basically, while the voltage is forced, voltage and current measurements are obtained simultaneously over several cycles. The magnitude and phase of the DUT impedance is extracted from the discrete Fourier transform (DFT) of a ratio of the resultant voltage and current sinusoids. This narrow-band information can be collected at varying frequencies (10mHz to 10Hz) to create a complex, multi-element model of the DUT. The resulting output parameters include the impedance (Z), phase angle (θ), capacitance (C), conductance (G), resistance (R), reactance (X), and the dissipation factor (D).

Because the very low frequency method works over a limited frequency range, the capacitance of the device under test (DUT) should be in the range of 1pF to 10nF. Table 1 summarizes the VLF C-V specifications (see Appendix A for complete specifications).

Table 1. Very Low Frequency C-V specifications

| Measurement Parameters | Cp, Gp, F, Z, θ, R, X, Cs, Rs, D, time |

| Frequency Range | 10mHz to 10Hz |

| Measurement Range | 1pF to 10nF |

| Typical Resolution | 3.5 digits, minimum typical 10fF |

| AC Signal | 10mV to 3V RMS |

| DC Bias | ±20V on the High terminal, minus the AC signal, 1µA maximum |

Required Hardware for VLF C-V Measurements

To make very low frequency impedance measurements, the following hardware is required:

- Model 4200-SCS with KTEI 9.0 or later software

- Two Model 4200 SMU instruments (Model 4200-SMU or Model 4210-SMU)

- Two Model 4200-PA Preamps

- Optional: Model 4210-CVU Capacitance Voltage Unit (for making high frequency C-V measurements)

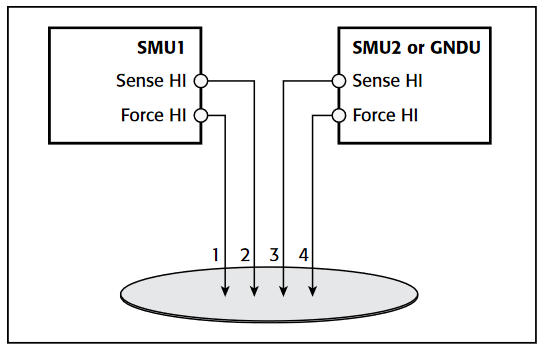

Making Connections to the Device

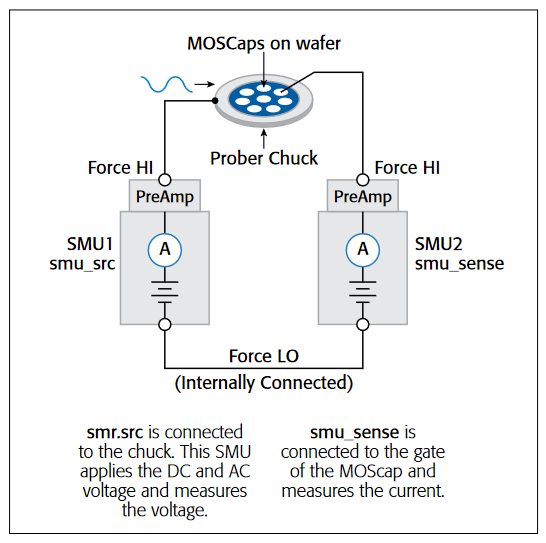

To make VLF C-V measurements on a device, connect the DUT between the two Force HI terminals of two SMU instruments (either Model 4200-SMU or Model 4210-SMU) with Model 4200-PA Preamps (Figures 1, 2). The preamp option is necessary because measuring very high impedances requires measuring very small currents. With the Model 4200-PAs, currents of <1E-12A can be measured. Because the VLF C-V method requires measuring small currents, it is best to use the triax cables that come with the SMU instruments to make these connections. The method does not support any switching instrumentation between the SMU instrument preamp and the device under test (DUT). One SMU outputs both the DC and AC voltage (SMU1 in Figures 1 and 2) and measures the AC voltage. The other SMU instrument measures the AC current (SMU2 in Figures 1 and 2). The SMU instrument used to measure the AC current should be connected to the high impedance terminal of the device (Figure 2).

An example of a MOSCap circuit connected for VLF C-V measurements is shown in Figure 2. Most MOSCaps have only a single pad on the top of the wafer, with the backside of the wafer used as the common contact for all MOSCaps. SMU1 outputs the AC+DC voltage and is connected to the chuck. The SMU that outputs the voltage is known as "smu_src" in the software that is included with the system. The high impedance terminal of the MOSCap is the gate and is connected to SMU2, which is called "smu_sense" in the software.

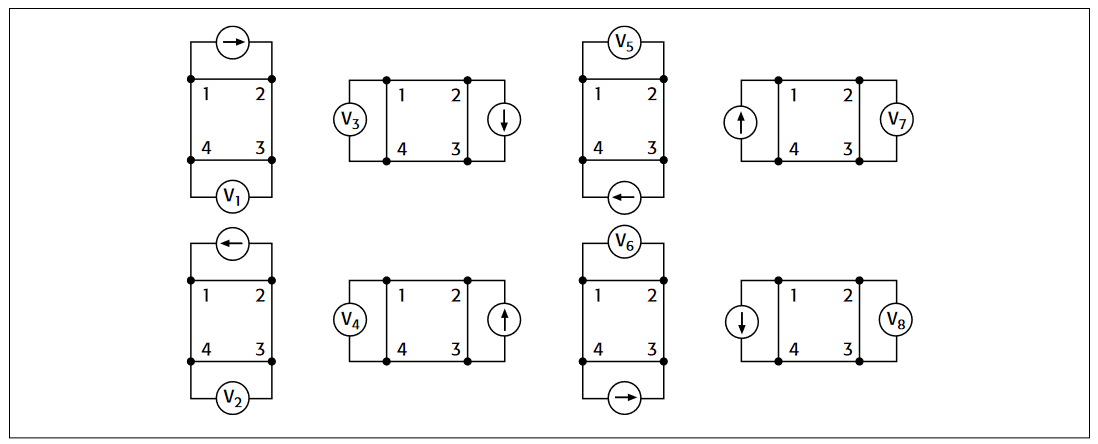

Using the KTEI Software to Perform VLF C-V Measurements

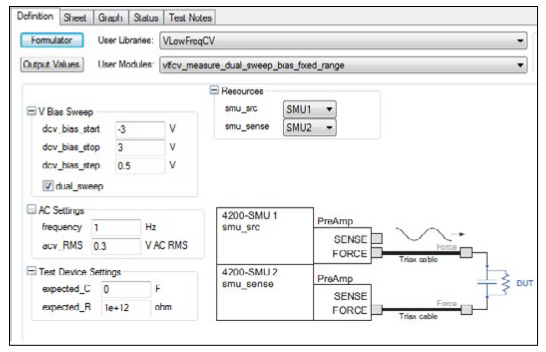

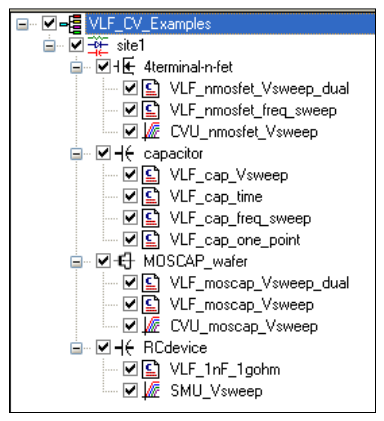

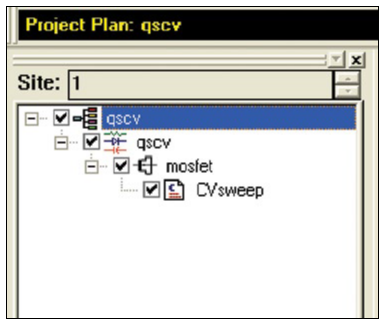

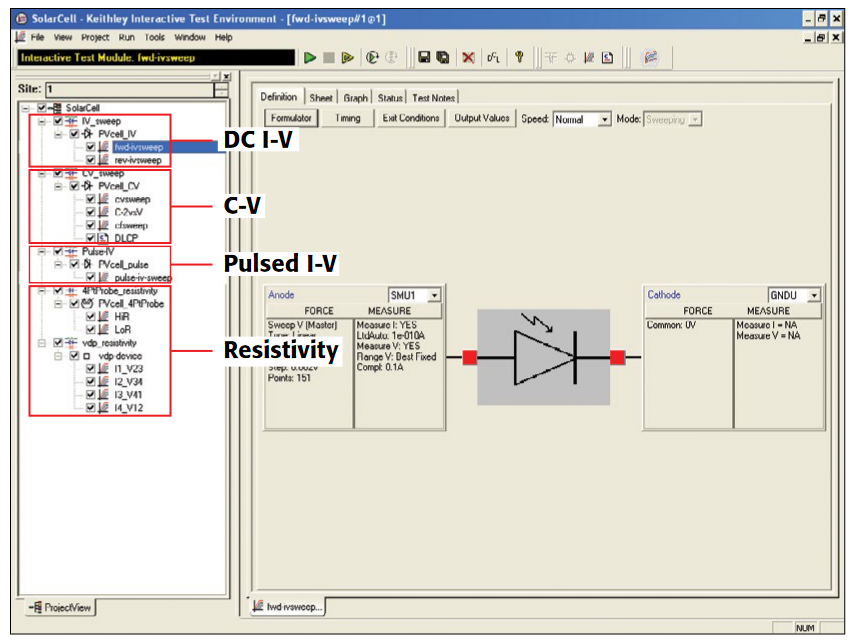

The system software includes five user modules and a project to make very low frequency C-V measurements. The user modules, listed in Table 2, are located in the VLowFreqCV User Library. The modules can be opened up as a User Test Module (UTM) within a project. KTEI 9.0 or later includes the VLF_CV_Examples project with the tests and results contained in the project (in the C:\s4200\kiuser\Projects\_CV project directory). This project (Figure 4) shows tests and data for a MOSFET, capacitor, MOSCap, and a test device consisting of a parallel RC combination. To run a test in the project, see "Testing a Device with VLF C-V."

Table 2. User Modules in the VLowFreqCV User Library.

| User Module | Description |

| vlfcv_measure | Measures C, G, Z, theta, R+jX at a fixed DC bias. |

| vlfcv_measure_dual_sweep_bias | Measures C, G, Z, theta, R+jX, time while sweeping the DC voltage. Optional dual sweep allows sweeping from dcv_bias_start to dcv_bias_stop, with 1 measure point at dcv_bias_stop, then back down to dcv_bias_start. |

| vlfcv_measure_dual_sweep_bias_fixed_range | Measures C, G, Z, theta, R+jX, time while sweeping the DC voltage. Measurements are made on a fixed current range which is determined by the expected_C, expected_R and maximum DC voltage. Optional dual sweep allows sweeping from dcv_bias_start to dcv_bias_stop, with 1 measure point at dcv_bias_stop, then back down to dcv_bias_start. |

| vlfcv_measure_sweep_freq | Measures C, G, Z, theta, R+jX, time at multiple user-specified test frequencies. |

| vlfcv_measure_sweep_time | Measures C, G, Z, theta, R+jX, time as a function of time. |

Once you've added a new module to a project, you need to input a few parameters. Many of the parameters are common to all five modules; however, each module has some unique parameters. Figure 3 illustrates the Definition tab of the vlfcv_measure_dual_sweep_bias_ fixed_range User Module showing all the user-defined parameters. The adjustable parameters for all the modules are listed in Tables 3 through 6.

The values of the expected capacitance (expected_C) and the expected parallel resistance (expected_R) determine which current range will be used to make the measurement. However, choosing specific values is generally not required, as setting expected_C = 0 will allow the test routines to estimate the C and R to use.

The simplest module is vlfcv_measure. It is used in the capacitor VLF_cap_one_ point test in the VLF_CV_Examples project. This test performs a single measurement. The module does not perform any sweeping, but it allows for all test parameters to be controlled (Table 3). Note that the maximum voltage possible is a combination of both the AC and DC voltages. The maximum negative DC bias voltage = -20 + (acv_RMS * √2 ). The maximum positive DC bias voltage = +20 - (acv_RMS * √2 ). Use expected_C = 0 to have the routine auto-detect the estimated C and R values.

Table 3. Adjustable parameters in vlfcv_measure User Module.

| Parameter | Range | Description |

| smu_src | SMUn | SMU instrument to source DC + AC voltage waveform and measure AC volts: SMU1, SMU2, SMU3… |

| smu_sense | SMUn | SMU t instrument o measure AC current: SMU1, SMU2, SMU3… |

| frequency | 0.01 to 10 | Test frequency in hertz, from 0.01 to 10. |

| Expected_C | 1e-12 to 1e-8 | Estimate of DUT capacitance in Farads, use 0 for auto-detect of DUT C and R. |

| Expected_R | 1e6 to 1e14 | Estimate of resistance parallel to DUT, in ohms |

| acv_RMS | 30e-3 to 3 | AC drive voltage in volts RMS |

| dcv_bias | ±20 less (acv_RMS * √2) | The DC voltage applied to the device |

Table 4. Adjustable parameters in the vlfcv_measure_dual_sweep_bias_fixed_range user modules.

| Parameter | Range | Description |

| smu_src | SMUn | SMU instrument to source DC + AC voltage waveform and measure AC volts: SMU1, SMU2, SMU3… |

| smu_sense | SMUn | SMU t instrument o measure AC current: SMU1, SMU2, SMU3… |

| frequency | 0.01 to 10 | Test frequency in hertz, from 0.01 to 10. |

| Expected_C | 1e-12 to 1e-8 | Estimate of DUT capacitance in Farads, use 0 for auto-detect of DUT C and R. |

| Expected_R | 1e6 to 1e14 | Estimate of resistance parallel to DUT, in ohms |

| acv_RMS | 30e-3 to 3 | AC drive voltage in volts RMS |

| dcv_start | ±20 less (acv_RMS * √2) | Starting DC voltage of the sweep |

| dcv_stop | ±20 less (acv_RMS * √2) | Stop DC voltage of the sweep |

| dcv_step | ±20 less (acv_RMS * √2) | Step size of the DC voltage. Number of steps limited to 512. |

| dual_sweep | 0 or 1 | Enter 0 for single sweep; enter 1 for dual sweep |

Table 5. Adjustable parameters in the vlfcv_measure_dual_sweep_freq user module.

| Parameter | Range | Description |

| smu_src | SMUn | SMU instrument to source DC + AC voltage waveform and measure AC volts: SMU1, SMU2, SMU3… |

| smu_sense | SMUn | SMU t instrument o measure AC current: SMU1, SMU2, SMU3… |

| frequency | 0.01 to 10 | Array of Test frequencies in Hertz.Maximum number of entries limited to 512, from 0.01 to 10. |

| Expected_C | 1e-12 to 1e-8 | Estimate of DUT capacitance in Farads, use 0 for auto-detect of DUT C and R. |

| Expected_R | 1e6 to 1e14 | Estimate of resistance parallel to DUT, in ohms |

| acv_RMS | 30e-3 to 3 | AC drive voltage in volts RMS |

| dcv_bias | ±20 less (acv_RMS * √2) | The DC voltage applied to the device |

Table 6. Adjustable parameters in the vlfcv_measure_sweep_time user module.

| Parameter | Range | Description |

| smu_src | SMUn | SMU instrument to source DC + AC voltage waveform and measure AC volts: SMU1, SMU2, SMU3… |

| smu_sense | SMUn | SMU t instrument o measure AC current: SMU1, SMU2, SMU3… |

| frequency | 0.01 to 10 | Test frequency in hertz, from 0.01 to 10. |

| Expected_C | 1e-12 to 1e-8 | Estimate of DUT capacitance in Farads, use 0 for auto-detect of DUT C and R. |

| Expected_R | 1e6 to 1e14 | Estimate of resistance parallel to DUT, in ohms |

| acv_RMS | 30e-3 to 3 | AC drive voltage in volts RMS |

| dcv_bias | ±20 less (acv_RMS * √2) | The DC voltage applied to the device |

| num_points | 1 to 512 | Number of points to take as a function of time |

Once the test is executed, several test parameters will be returned to the Sheet tab and can be saved as an .xls file. These test parameters can also be plotted on the Graph tab. Table 7 lists the returned test parameters and their descriptions. From these returned test parameters, more device extractions can be performed using the mathematical functions in the Formulator.

Note that the tests return all typical C-V measurement parameters. For example, both Cp-Gp and Cs-Rs are always returned, even if the test device response only matches the parallel model (Cp-Gp).

Table 7. Measurements returned for the modules in the VLowFreqCV library.

| Returned Test Parameters | Description |

| Status | Error code from test module execution. Definitions of the returned errors are listed at the bottom of the Definition tab in the UTM Description |

| times | Calculated time difference between readings. |

| dcv_bias | Programmed DC voltage applied to the device. |

| meas_Cp | Measured capacitance in parallel model (Cp-Gp). |

| meas_Gp | Measured conductance in parallel model (Cp-Gp) |

| meas_freq | Measured test frequency. |

| meas_Z | Measured impedance (Z-theta) |

| meas_Theta | Measured phase angle in degrees (Z-theta). |

| meas_R | Real component of the impedance (R + jX). |

| meas_X | Imaginary component of the impedance (R + jX). |

| meas_Cs | Measured AC capacitance in series model (Cs-Rs). |

| meas_Rs | Measured resistance in series model (Cs-Rs). |

| meas_D | Calculated dissipation factor, D. |

| meas_irange | The SMU instrument current range that the measurement was taken. |

Using the VLF_CV_Examples Project

The VLF_CV_Examples project that comes with KTEI 9.0 or later has examples of VLF C-V measurements on various devices.This project is located in the "_CV" folder in the 4200 projects directory (c:\S4200\projects\_CV). The project has several UTMs that employ the user modules in the VLowFreqCV library.The project tree of the VLF_CV_Examples project is shown in Figure 4. The project contains tests for making both low frequency C-V measurements using the VLF C-V technique and also high frequency C-V measurements using the Model 4210-CVU Capacitance Voltage Unit. It also has one I-V test for initial screening of leakage current for test devices with unknown characteristics.

Even though the project has tests for specific devices, the VLF C-V user modules can be used on a variety of devices. The particular devices measured in the project are an n-MOSFET (gate to source/drain/bulk), a capacitor, a MOScap, and a parallel RC combination.

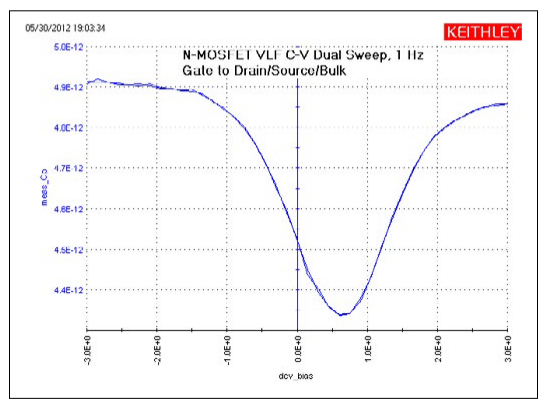

MOSFET

In the VLF_CV_Examples project, there are three tests for the n-fet devices: two UTMs and one ITM. Figure 6 shows the results of generating a very low frequency dual C-V sweep on an n-MOSFET measured between the Gate terminal and the Drain/Source/Bulk terminals tied together (Figure 5). This C-V sweep is in the VLF_nmosfet_Vsweep_dual UTM. Tests for measuring capacitance as a function of frequency (VLF_nmostfet_ freq_sweep), as well as a high frequency C-V test (CVU_nmostfet_ freq_sweep, taken with the Model 4210-CVU) are also included in the project.

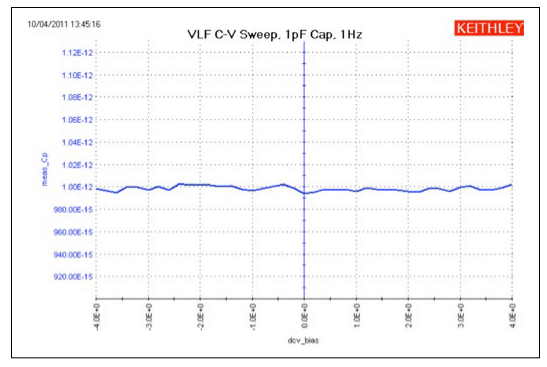

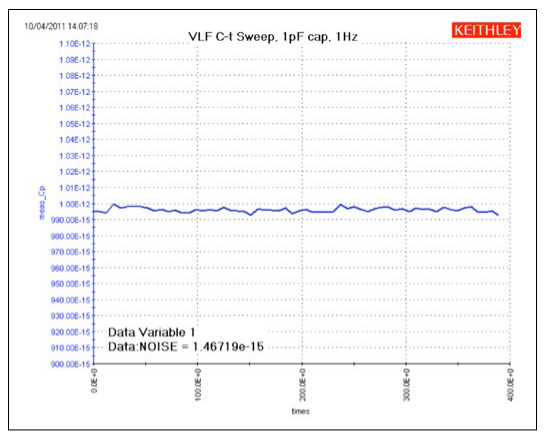

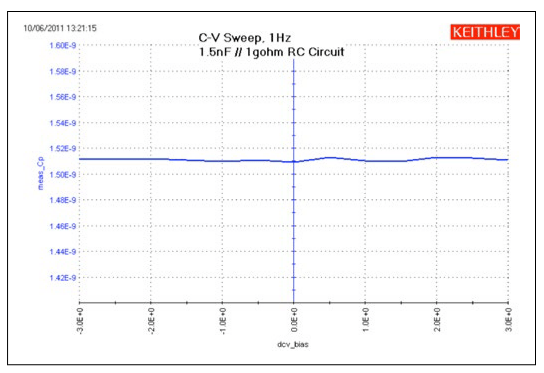

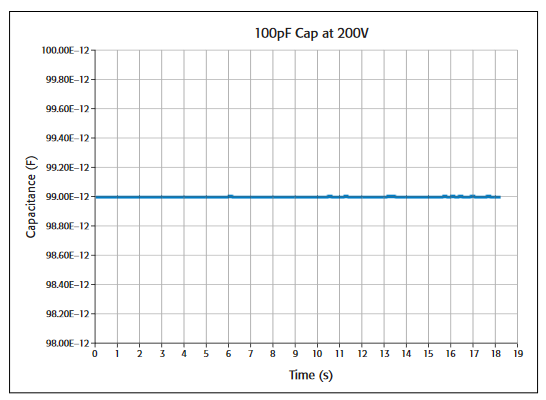

Capacitor

Using the VLF C-V method, capacitors can be measured in the range of 1pF to 10nF. The project has four UTMs (Figure 7).The VLF_cap_time UTM example in the project measures the capacitance of a 1pF capacitor as a function of time Figure 4. Project tree of VLF_CV_Examples project (Figure 10). The results of measuring the 1pF capacitor are shown in Figure 9. This small capacitance was measured at a test frequency of 1Hz with capacitance measurement noise levels at less than ±5E-15F. The Formulator can be used to determine the noise and average capacitance readings easily.

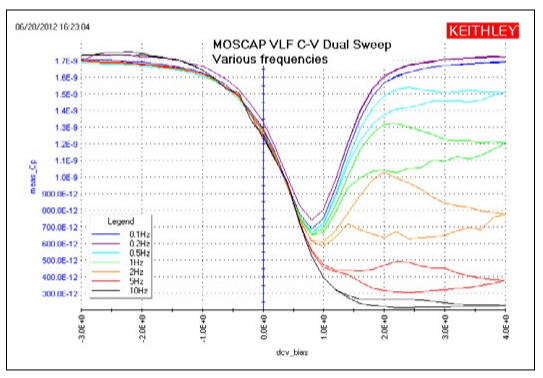

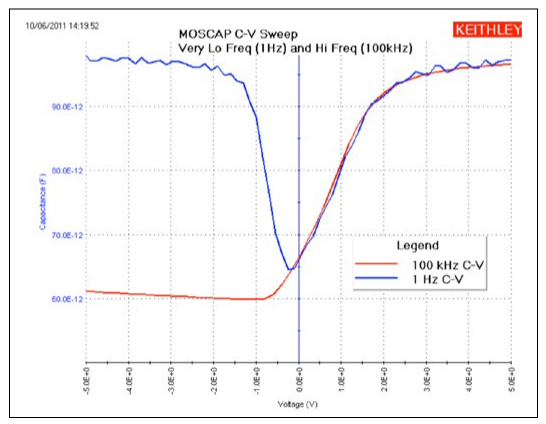

MOScap

The MOScap device has three tests; all are DC bias sweeps with two using SMUs for the VLF C-V test DC bias voltage sweep (VLF_moscap_Vsweep_dual and VLF_moscap_Vsweep) and the other using the 4210-CVU for higher frequency testing (CVU_moscap_Vsweep). An example of a MOScap VLF-CV dual sweep generated with various test frequencies ranging from 0.1 Hz to 10 Hz is shown in Figure 11. This test was performed on a chuck at room temperature. This sweep is the result of executing the VLF_moscap_Vsweep_dual UTM in the project. From the low frequency C-V data, characteristics about the MOScap can be determined. The built-in math functions are helpful in performing the analysis of these devices from the C-V data. The connection diagram for the MOSCap is shown in Figure 2. The dual sweep functionality aids in determining any hysteresis behavior in the inversion region of the MOScap device, where frequency dependence is also observed. Note that the SMU instrument measuring the low current is not connected to the chuck. Connecting the sensitive (i.e., low-current measurement) instrument to the chuck will result in noisier measurements.

In addition to the UTM that generates VLF C-V measurements on the MOScap, the project includes an ITM to measure high frequency C-V on the MOScap. The high frequency C-V measurements were generated using the Model 4210-CVU, which has a test frequency range of 1kHz to 10MHz, with the example data taken at 100kHz.

To compare the results of both low and high C-V measurements on one graph, the data can be copied from one test module into another. Just select and copy the C-V measurements from the Sheet tab of one test module and then paste the data into the columns of the CALC Sheet of the other test module.The data in the CALC Sheet can be selected on the graph to plot.To do this, make sure to check the "Enable Multiple Xs" box in the Graph Definition window. An example showing both the low and high frequency C-V measurements on one graph is shown in Figure 12.

Parallel RC Device

Some devices can be modeled as a parallel RC combination (connection diagram in Figure 13). The parallel resistance is usually the leakage resistance of the device. There are two tests for the RC device: one is the UTM for a VLF C-V DC bias sweep (VLF_1nf _1gohm) and the other is an ITM V sweep (SMU_Vsweep). Figure 14 shows the results of performing a low frequency sweep on a 1.5nF and 1GW parallel combination.From the bias voltage and the resistance (1/Gp) of the device,the current was calculated in the Formulator and displayed on the graph. Excessive leakage current can cause erroneous results if the current exceeds the maximum current range for the particular RC combination. To determine the DC leakage current of an unknown DUT, use the ITM SMU_Vsweep, as described in the section titled "Testing a Device with VLF C-V." More information about making optimal results is described in the next section of this note.

Testing a Device with VLF C-V

Dissipation Factor

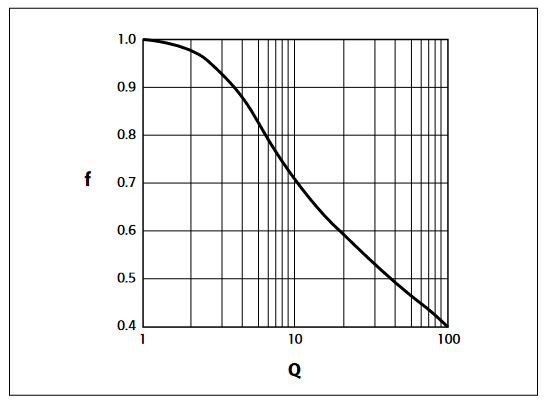

The parallel resistance of the device under test is a key aspect that determines the quality of the capacitance measurement because it causes additional DC current to flow, which reduces measurement accuracy. This parallel resistance at a given frequency is otherwise expressed as D, the dissipation factor.Here is the equation for the simple parallel model.

D = Reactance/Resistance = 1/ωRC = 1/2pfRC

where:

f is the test frequency, in Hz

R is the parallel resistance of the test device, in Ω

C is the capacitance of the test device, in farads

Guidance for measurement performance across a range of D values is shown in Table 8. As the table shows, higher D values reduce the accuracy of the reported C measurement.

"Not Recommended" means that the typical error is >10%.For details on specific capacitance and frequency values, see the VLF C-V Typical Specifications in Appendix A.

If the device is purely capacitive (very low to almost no leakage current, a D <0.1), then just connect the DUT as shown in Figure 8 (or Figure 2 if the DUT is on a wafer). After connection, run the desired test(s). However, if the device type is new, or its electrical characteristics are unknown, then use the following procedure. This procedure provides a guideline for determining reasonable parameter values for unknown test devices using the parallel model (Figure 13). It also provides guidance for evaluating results.

Table 8. VLF C-V typical accuracy vs. D and current measure range for the sense SMU instrument.

| 0.01 D | 0.1 D | 1 D | 10 D | |

| 1 µA | 0.6 % | 1.6 % | Not Recommended | Not Recommended |

| 100 nA | 1.4 % | 10 % | Not Recommended | Not Recommended |

| 10 nA | 0.7 % | 4 % | 6 % | Not Recommended |

| 1 nA | 0.4 % | 2 % | 2.6 % | 3 % |

| 100 pA | 0.8 % | 0.6 % | 0.6 % | 2 % |

Setup

- Connect the DUT as shown in Figure 2. The connection must be direct with the supplied triax cables. No switching or Model 4225-RPMs may be in the cable path from the SMU instrument PreAmp to the DUT. The VLF C-V method utilizes low current measurements, so ensure that appropriate shielding and guarding are used. Use triax cable and eliminate, if possible, or minimize any unshielded or unguarded cable runs. For on-wafer measurements, use triax probe manipulators and guarded probe arms.

- Open the VLF_CV_Examples project (in c:\S4200\projects\_CV). Create a new version of the project by renaming it by using the menu option File | Save Project As.

- Choose the SMU instrument IV sweep, SMU_Vsweep, under the RCdevice node. Choose voltage start and stop values for the sweep that match the desired minimum and maximum DC bias voltages to be used for VLF C-V tests. This test will help determine if the DUT leakage is too high for repeatable,accurate results.

- Run the SMU_Vsweep test. Review the results on the graph or in the Sheet. For best results, the maximum current shouldcbe <±1µA. If the current >±1µA, reduce the bias voltages until the current <±1µA. Note these voltages for later testing.These voltages may need to be adjusted again as described later in this procedure.

- Next, choose the VLF_cap_ freq_sweep test, under the capacitor device in the project tree. Enter the desired test frequencies, using just five to ten points to span the desired frequency range. If only one test frequency is desired, use the single point test VLF_cap_one_ point instead. Use the default expected_C = 0 and expected_R = 1E+12. Use acv_RMS = 0.3V and dcv_bias = 0.0V. This test will help determine the dissipation factor D of the DUT.

- Run the VLF_cap_ freq_sweep test. Review the results in the Sheet. Review the value(s) in the meas_D column. If |meas_D| <1, then the results are reasonable for the test frequencies and DC bias values that had <±1µA with the SMU_Vsweep test. If |meas_D| <10 then results should be reasonable for dcv_bias = 0V. If |meas_D| >10, then this present implementation of VLF C-V may provide unacceptable results or results with fairly large errors (see Table 8). Note that reasonable values with a low D value at dcv_bias = 0 may provide larger errors as the DC bias is increased.

- Configure the desired test, such as the bias sweep VLF_cap_Vsweep (Table 4) or frequency sweep VLF_cap_ freq_sweep (Table 5). Use the voltage values determined in the previous step. As stated earlier, using expected_C = 0 will perform an auto-detect of both the C and R values. For the other parameters, follow the description in the table corresponding to the test (Tables 3 through 6).

- Run or append the test. Running the test (green triangle) will discard the previous test data. The

append button (yellow triangle just to the right of the green run icon) will keep the old data, allowing

for comparison across multiple tests. The test parameters used for each append are in the Settings tab

of the Sheet. For unknown or new devices, review the measurements to ensure that the results are

reasonable by evaluating the data in the Sheet as well as the plotted values.

- Review the plotted data, noting the overall shape and Y-axis values.

- Check the status returned from the test. Status = 0 means that the routine did not detect any errors, but the validity of the data must still be assessed; go to the next step. If there is a non-zero status value, refer to the Table 9 Error Codes to see the explanation and troubleshooting suggestions.

- In the Sheet, check the current measurement range used.The column meas_irange, located on the right side of the Sheet, shows the current measure range used for each point. If this range is 1E-6 (1µA) or lower, skip to the next step. If any of the measure range values is 10E-6 (10µA) or larger, the results for these rows are suspect. Change the DC bias voltage to reduce the current measure range used for the test. For example, when running a voltage bias sweep, reduce the start and stop voltage used, for example from ±5V to ±2V, and re-run the test. Verify that the new test uses a meas_irange 1E-6 (1µA) or lower, then compare the results to the previous run taken with the 10µA range. Generally, the results with the 1 µA range are more accurate.

- If the Y-axis scale shows the maximum of 7E22 or 70E21, then an overflow has occurred on one or

more measurements in the test. Review the data in the Sheet, in the meas_Cp column, for entries

of 70E21 or 7E22. There are a few causes of the overflow:

- If the overflow values are only at the start and end of the test, consider reducing the range of sweep values to omit the sweep points that cause the overflow values. Another option is to specify appropriate values for expected_C and expected R. Before choosing values for expected_C and expected_R, let's briefly explain how these values affect the test. If the overflow values are most or all of the rows in the meas_Cp column, it is possible that an incorrect measure range was used for the test. This means that the current measure range used for the test was too small for the test parameters and DUT. The measure range used for the test is contained in the meas_irange in the Sheet. The current measure range for the sense SMU instrument is based on the expected_C and expected_R values.

- To change the current measure range for a test, supply an expected_C value that is larger than the meas_Cp value. Review the values in the meas_Cp column and choose a representative, non-overflow value and use it to calculate the expected_C = 2 * chosen meas_Cp value.To choose a value for expected_R, review the meas_Gp column for a representative value. Set expected_R = 1/(2* chosen meas_Gp).

- If one or more of the meas_Cp values is negative:

- Ensure that the DUT connections are good.

- The D may be too high, or the DC current leakage is too high compared to the capacitance

- Review the Sheet for meas_D and meas_irange values.If D > ~10 and or meas_irange is ≥10nA, the results may have a larger error

- Consult Table 8. Compare the current measure range (in the meas_irange) column to the corresponding row in Table 8. Note that the higher D values are more difficult to test.

- Try one or more of the following adjustments: a) reduce the DC bias voltage; b) increase the acv_RMS = 0.3V; c) increase the test frequency

- If the meas_Cp values seem noisy or inconsistent,append several tests with identical parameter values and review the data. If the results are different across each run, this indicates that the system is operating at or near the noise floor, which means that the capacitance value of the test device is small, or the test device has a higher D value (Table 8)

- If none of these adjustments provides reasonable results, try a higher frequency C-V test using the 4210-CVU, if available

- Add tests, such as the capacitance vs. time (test VLF_cap_time) or more DC bias sweeps at additional test frequencies.Recall that data may be saved in .xls or .csv file formats by using the Save As button on the Sheet, or on the Graph tab by clicking the Graph Settings button in the upper right corner and choosing Save As.

Initial Screening of DUT characteristics

Table 9. VLF C-V error codes and descriptions

| Error Code | Description | Explanation and Troubleshooting Recommendation |

| 0 | Test executed with no errors | No software or operational errors were detected. |

| -16001 | smu_src is out of range | Specified SMU instrument is not available in the chassis. For example, if SMU5 is entered, but there are only four SMU instruments in the 4200 chassis, then this error will occur. Modify SMU instrument string to an available SMU instrument number: SMU1, SMU2, SMU3.. |

| -16002 | smu_sense is out of range | Specified SMU instrument is not available in the chassis. For example, if SMU5 is entered, but there are only four SMU instruments in the 4200 chassis, then this error will occur. Modify SMU instrument string to an available SMU number: SMU1, SMU2, SMU3 |

| -16003 | Frequency is out of range. | Ensure that the test frequency is within the range of 10mHz to 10Hz, inclusive |

| -16004 | acv_RMS is out of range | Make sure that the RMS voltage is within the range of 0.01V to 3.0V, inclusive |

| -16005 | dcv_bias is out of range | Modify the DC or AC voltage bias to ensure that the ±20V maximum is not exceeded. Maximum negative voltage = –20 + (AC voltage *) Maximum positive bias voltage = 20 – (AC voltage * √2) |

| -16006 | hold_time is out of range | This error is unused for the VLowFreqCV routines |

| -16007 | delay_time is out of range | This error is unused for the VLowFreqCV routines. |

| -16008 | Too few points per period | This error indicates that the test was aborted by the operator. |

| -16009 | Output array sizes are not equal, or are larger than 4096. | Make sure all output array sizes are the same value and are not greater than 4096. |

| -16010 | Over range indication detected. | Current measurement over-range occurred and returned values are set to 7E22 (70E21).Troubleshooting: Review the value in the meas_CP column of the Sheet, looking for the overflow values (7E22 or 70E21). Follow the process given in Step 8d. |

| -16011 | Results array size is less than the number of points in the sweep. | Increase the size of all output arrays to be equal to the number of points in the sweep |

| -16012 | Could not collect enough data to perform measurement. | Cannot estimate expected_C or expected_R.This error occurs only when expected_C = 0.Input a estimated non-zero value for expected_C.Review the meas_Cp values in the Sheet for non-overflow values. Set estimated_C = 2 * nonoverflow meas_Cp |

| -16013 | Unable to allocate memory. | This error is unused for the VLowFreqCV routines. |

| -16014 | Current range is out of range | This error is unused for the VLowFreqCV routines. |

| -16015 | Irange_sense and expected_C cannot be 0 at the same time | This error is unused for the VLowFreqCV routines. |

| -16016 | Expected_C is out of range | Expected_C must be 0 (auto-detect C) or between 1E-15 and 1E-3, inclusive. |

| -16017 | This test requires preamp is connected to smu_sense | Make sure preamp is connected to each SMU used in the test. If reconnecting preamps, run run KCON and choose "Update PreAmp and RPM Configuration" in the Tools menu. |

| -16018 | Invalid start, stop, step DC bias sweep values. | Correct the values for the voltage bias sweep.dcv_bias_step cannot be 0, unless dcv_bias_start = dcv_bias_stop. If dcv_bias_start = dcv_bias_stop, then dcv_bias_step must = 0 |

| -16019 | Output array sizes are less than number of points in sweep. | Increase the size of all output arrays to be equal to the number of points in the sweep. |

| -16020 | Invalid combination of start, stop, step dc bias sweep values. | Correct the values for the voltage bias sweep.dcv_bias_step cannot be 0, unless dcv_bias_start = dcv_bias_stop. If dcv_bias_start = dcv_bias_stop, then dcv_bias_step must = 0. |

Guidelines for Making Optimal Measurements and Troubleshooting Techniques

When making high impedance, very low frequency C-V measurements using the SMU instruments, various techniques must be used to optimize measurement accuracy. These techniques include implementing low current measurement practices and choosing the appropriate settings in the software.

Implementing Low Current Measurement Techniques

Because using the very low frequency impedance measurement method involves measuring picoamp to femtoamp current levels,low current measurement techniques must be implemented.Use the triax cables that come with the Model 4200-SCS, which are shielded and will allow making a guarded measurement, if necessary. To reduce the noise due to electrostatic interference,make sure the device is shielded by placing it in a metal enclosure with the shield connected to the Force LO terminal of the Model 4200-SCS. Detailed information on low current measurement techniques can be found in Keithley’s Low Level Measurements Handbook. Also, ensure that the triax cable is directly connected to the DUT or probe pins; do not use any switching matrix or Model 4225-RPM in the SMU instrument signal path.

Choosing the Correct "expected_C" and "expected_R" Values

In most cases, expected_C should be 0 and the expected_R = 1E12 (both are the default values). When expected_C = 0, the VLF C-V routine will determine estimated values for both C and R of the device under test. The estimated R and C values determine the SMU instrument measurement range. If these values are chosen incorrectly, measurement errors or measurement range overflow may result (see Table 9, error code -16010 for more information). However, in some cases, entering a non-zero estimated capacitance for expected_C may provide better results for higher D devices or larger DC bias tests. To calculate a value of expected_C, multiply a non-overflow value from the meas_Cp column by two and enter this value into the test definition expected_C.

To determine if a device is compatible with the present VLF C-V approach, measure the DC resistance of the DUT, performing an I-V test using the SMU_Vsweep test under the RCdevice of the project tree of the VLF_CV_Examples project. Use the same test voltages in the I-V sweep that will be used in the impedance measurements. Additionally, performing a single measurement (test VLF_cap_one_ point) or frequency sweep (test VLF_cap_freq_sweep) at a DC bias of 0V will determine the D of the device. Refer to Testing a Device with VLF C-V and Table 8 for additional information.

Conclusion

The Model 4200-SCS contains a tool for performing very low frequency C-V measurements using the SMU instruments and preamps. This method enables the user to perform low capacitance measurements at a precise test frequency in the range of 10mHz to 10Hz. The KTEI 9.0 or later software included with the system enables the user to execute these low impedance measurements easily and extract important parameters about the DUT. When combined with the Model 4210-CVU Capacitance Voltage Unit, the Model 4200-SCS offers the user a single system that can perform both high and low frequency measurements.

Using the Ramp Rate Method for Making Quasistatic C-V Measurements with the Model 4200-SCS Parameter Analyzer

Introduction

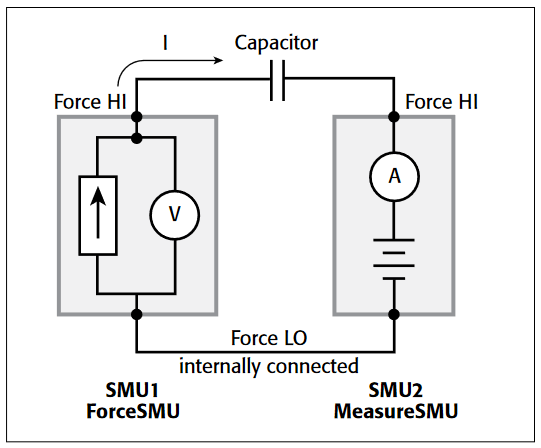

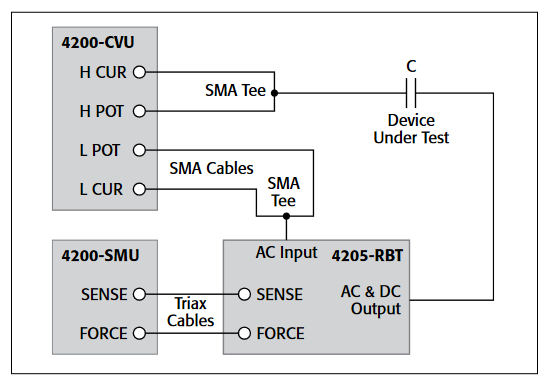

Capacitance-voltage (C-V) measurements are generally made using an AC measurement technique. However, some capacitance measurement applications require a DC measurement technique. These are called quasistatic C-V (or QSCV) measurements because they are performed at a very low test frequency, that is,almost DC. These measurements usually involve stepping a DC voltage and measuring the resulting current or charge. Some of the techniques used for quasistatic C-V measurements include the feedback charge method and the linear ramp method. The Model 4200-SCS Parameter Analyzer uses a new method, the ramp rate method, which employs two Model 4200-SMUs Source Measure Unit (SMU) Instruments with two Model 4200-PA PreAmps. The optional 4200-PA PreAmps are required because this test involves sourcing and measuring current in the picoamp range. The SMU instruments are used to source current to charge the capacitor, and then to measure the voltage, time, and discharge current.

The software calculates the capacitance as a function of voltage from the measured parameters and shows the curve on the Model 4200-SCS's display. The software to execute the ramp rate method is included in version 7.1 and higher of the Keithley Test Environment Interactive (KTEI) software. This application note describes how to implement and optimize quasistatic C-V measurements using the Model 4200-SCS and the ramp rate method. It assumes the reader is familiar with making I-V measurements with the Keithley 4200-SCS at the level outlined in the Model 4200-SCS Reference Manual.

Ramp Rate Method

Figure 1 illustrates the basic connection diagram for the ramp rate method. This configuration requires two 4200-SMUs with 4200-PAs connected to either side of the device under test. Because the ramp rate method works over a limited range, the capacitance of the device under test should be in the range of 1pF to about 400pF.

Basically, the ramp rate method works by charging up the device under test to a specific DC voltage using an SMU instrument as a current source. Once the device is charged up, a current of the opposite polarity is forced to discharge the device as the SMU instrument measures voltage as a function of time. A second SMU instrument measures the discharge current. From the measured voltage (V), current (I) and time (t) values, the capacitance (C) is derived as a function of voltage and time:

The ramp rate method included with the 4200-SCS follows these steps when making QSCV measurements:

- Charge the Device: A precharge current of 100pA is applied to the DUT by an SMU instrument, called ForceSMU, until the compliance voltage is reached. The compliance voltage is user specified and is called VStart. The polarity of the precharge current is the same as the polarity of the VStart voltage. If the precharge current is not sufficient to force the device to VStart, then a timeout error will be generated.

- Bias the Device for Specified Time Prior to Sweep: The device is biased at the VStart voltage for a user specified time (PreSoakTime) prior to the sweep.

- Apply Ramp Current to Discharge Device: Once the device is biased for a specified time,

a ramp rate current is applied to the device to discharge the device. The ramp rate current is of the

opposite polarity as the precharge current.The value of the ramp current is:

Iramp = CVal × RampRate

where:

CVal = the estimated capacitance value input by the user in farads (F).

RampRate = user input slope of stimulus voltage (dV/dt) in V/s.

- Simultaneously Trigger SMU Instruments to Take Measurements: The SMU instrument that is the ForceSMU measures voltage (V1, V2, T3 … Vn) and time (T1, T2, T3...Tn). The SMU instrument that is the MeasureSMU measures the current (I1, I2, I3 … In). The voltage, time, and current measurements are made until the opposite polarity of the VStart voltage is reached.

- Calculate Voltage, Time, and Capacitance Output Values: In real time, parameters are

extracted from the measurements and will appear in the Sheet or Graph. These parameters are

Vout = voltage, Tout = time, and Cout = capacitance, and are calculated

as follows:

Vout = (the average of two measured voltages)

Tout = T2 (the time when the second measurement is made)

Cout

where dV = V2 – V1 and dT = T2 – T1.

How to Make QSCV Measurements Using the KITE Software

The system's software includes a module to make quasistatic C-V measurements using the ramp rate method. This module, meas_qscv, located in the QSCVulib user library, can be opened up as a UTM from within a project.

Setting up the Parameters in the meas_qscv Module

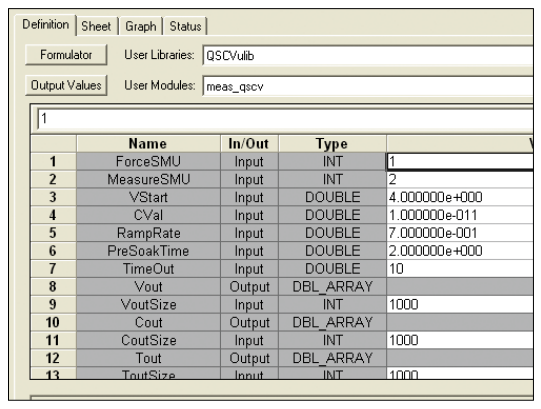

Once you've opened the module up into a project, you need to input a few parameters. The adjustable parameters for the meas_qscv module are listed in Table 1.

Table 1. List of Adjustable Parameters in meas_qscv Module

| Parameter | Range | Description |

| ForceSMU | 1-8 | SMU instrument number that will force current through capacitive load. This SMU instrument must have a preamp. |

| MeasureSMU | 1-8 | SMU instrument number that will measure current. This SMU instrument must have a preamp. |

| VStart | -200 to 200 | Starting and ending voltages (V) for C-V sweep. |

| CVal | 1E–12 to 400E–12 | Approximate capacitance of device under test in Farads (F). |

| RampRate | 0.1 to 1 | Slope of stimulus voltage (dV/dt) in V/s. |

| PreSoakTime | 0 to 60 | Additional time delay in seconds to allow DUT, fixture, and cables to charge up. |

| TimeOut | 10 to 60 | Time allowed in seconds to charge up prior to time out. |

Here's a more detailed description of the input parameters:

ForceSMU: The SMU instrument that will force current to the device under test and measure the voltage as a function of time. This SMU instrument must have a preamp because it will be sourcing current in the picoamp range.

MeasureSMU: The SMU instrument that will measure the current flow in the circuit. This SMU instrument must have a preamp because it will be measuring current in the picoamp range.

VStart: This is both the starting and ending voltage of the C-V sweep because the C-V sweep is always symmetrical about 0V.

CVal: Enter at least the approximate maximum capacitance value of the device under test. This value is used to determine the magnitude of the source current to charge the device.

RampRate: The slope of the stimulus voltage in V/s. If the ramp rate is too fast, there will not be enough data points in the sweep. If the ramp rate it too slow, the readings may be noisy. Some experimentation may be needed to find the optimal setting for a particular device.

PreSoakTime: The length of time in seconds to apply the VStart voltage to the device prior to the start of the C-V sweep. Specify sufficient time for the device to charge up and reach equilibrium.

TimeOut: The amount of time allowed to charge the device to the VStart voltage until the test module times out. In some cases, such as when a device is shorted, the device may not reach the VStart voltage; this parameter enables the module to stop automatically and generate an error message. By default, this is set to 10 seconds.

Executing the Test

The meas_qscv module can be opened up in a project using a UTM (User Test Module). However, Keithley has already created a project called qscv that makes quasistatic C-V measurements using this module. It can be found at the following address on the Model 4200-SCS's hard drive:

C:\S4200\kiuser\Projects\_CV

The project tree for the qscv project is shown in Figure 2.

This project contains a UTM called CVsweep for making C-V measurements on a MOSFET device. The Definition Tab of CVsweep UTM is shown in Figure 3.

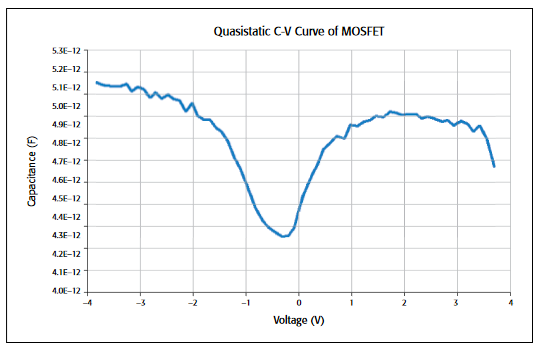

In this UTM, SMU1 (ForceSMU) and SMU2 (MeasureSMU) are used to make the C-V measurements. The VStart value is set to 4V, so this will generate a voltage sweep from –4V to 4V. The approximate capacitance value is 10pF, so this was entered as the CVal parameter. This CVal capacitance value will be used to determine the ramp rate current. If this number is too low (for example, 1E–12 instead of 10E–12), then the capacitance measurements will appear noisy. The RampRate value was set to 0.7V/s. In this case, a RampRate that is larger (1V/s) will produce a somewhat quieter curve but will have fewer data points. A RampRate that is smaller (0.1V/s) will produce a much noisier curve with lots of data points. You will need to experiment in order to determine the optimal settings for a particular device under test.

Once the device is connected to the two SMU instruments and the UTM is created with the desired input parameters, the C-V sweep can be executed. The results of such as sweep are shown in Figure 4.

Optimizing Measurements

When making quasistatic C-V measurements using the ramp rate method, various techniques must be used to optimize measurement accuracy. These techniques include implementing low current measurement practices and choosing the appropriate settings in the software.

Because using the ramp rate method involves sourcing and measuring picoamp-level current, low current measurement techniques must be implemented. Use the triax cables that come with the 4200-SCS, which are shielded and will allow making a guarded measurement. To reduce noise due to electrostatic interference, make sure the device is shielded by placing it in a metal enclosure with the shield connected to the Force LO terminal of the 4200-SCS. Detailed information on low current measurement techniques can be found in Keithley’s Low Level Measurements Handbook.

The parameter settings in the meas_qscv module that will most affect the measurements are CVal and RampRate. CVal is the approximate value of the device under test. If you input a value that is larger than that of the actual device, then the RampRate will be larger and there will be fewer data points. Conversely, if the capacitance value entered is smaller than the actual device capacitance, the RampRate will be lower and there will be more data points in the curve. Use the largest RampRate possible, but ensure the device curve appears settled. However, if the RampRate is too fast, there may not be enough points in the sweep.

To reduce the noise level of the curve, the moving average (MAVG) function in the Formulator can be used. Try using a moving average of three readings to see if this helps. Do not set the moving average number so large so that you lose the shape of your C-V curve.

To subtract the offset due to the cables and probe station, generate a C-V sweep using the meas_qscv module with the probes up or with an open circuit in the test fixture. Using the Formulator, take an average of the readings. Subtract this average offset value from capacitance measurements taken on the device under test.

Conclusion

Quasistatic C-V measurements can be made with the 4200-SMUs using the ramp rate method. This technique is implemented in software in the meas_qscv module of the QSCV_uslib user library of the 4200 KITE software. Using low level measurement techniques and choosing the appropriate parameter settings in the software will ensure optimal results.

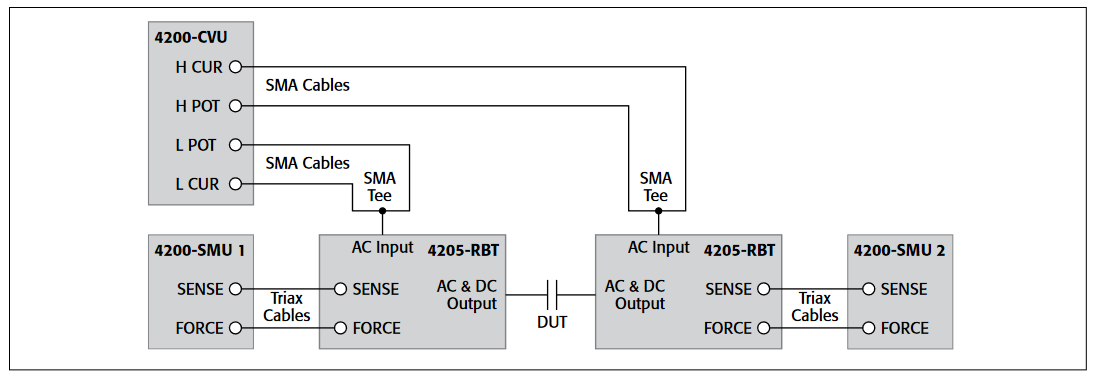

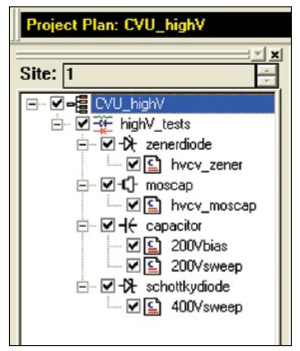

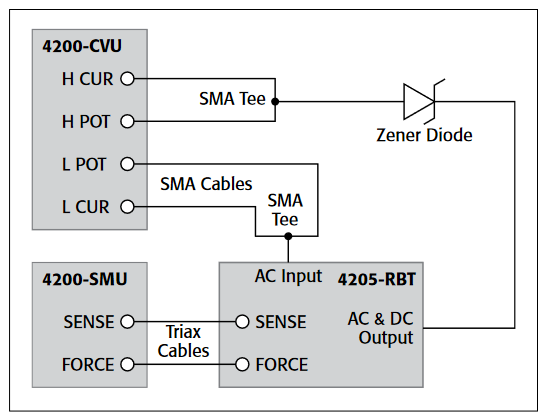

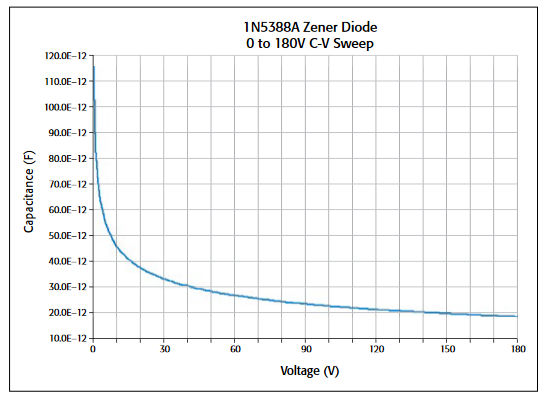

Using the Model 4200-CVU-PWR C-V Power Package to Make High Voltage and High Current C-V Measurements with the Model 4200-SCS Parameter Analyzer

Introduction

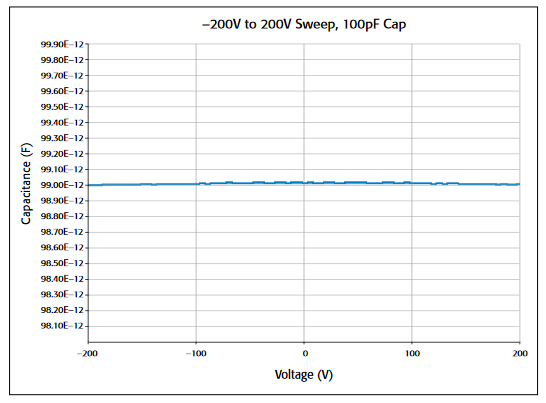

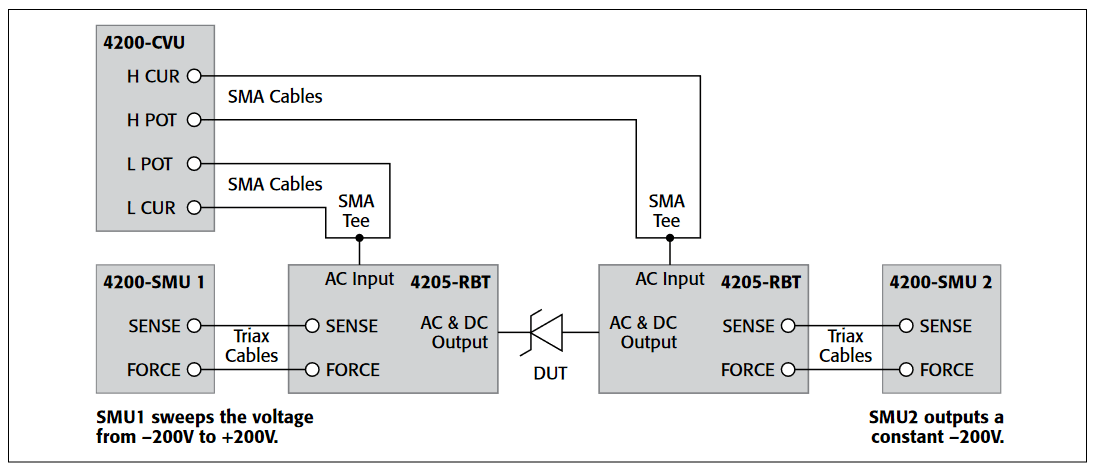

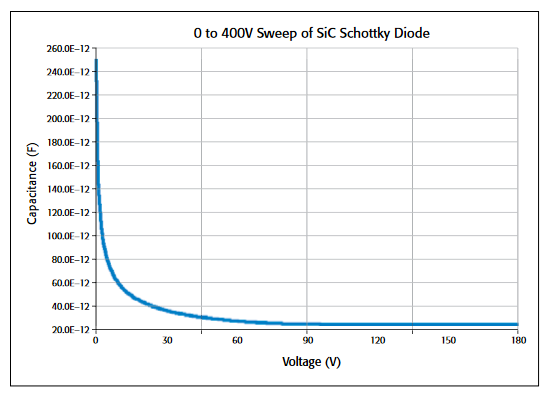

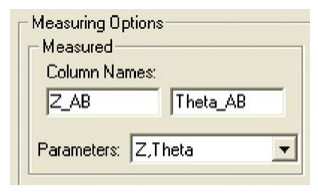

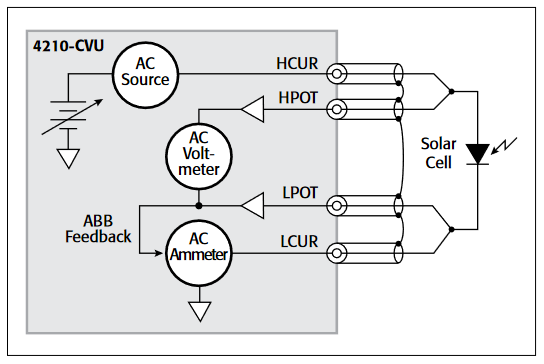

Traditional capacitance-voltage (C-V) testing of semiconductor materials is typically limited to about 30V and 10mA DC bias. However, many applications, such as characterizing C-V parameters of LD MOS structures, low k interlayer dielectrics, MEMs devices, organic TFT displays, and photodiodes, require higher voltage or higher current C-V measurements. For these applications, a separate high voltage DC power supply and a capacitance meter are required to make the measurements.