はじめに

デジタル・テレビ革命の火付け役ともいわれるHDMI(HighDefinition Multimedia Interface)技術が、広く普及しつつあります。コンテンツ・プロバイダ、システム・オペレータ、家電メーカなどが、規格の普及を後押ししています。その結果、規定されたテストによって、HDMI規格へのコンプライアンスを証明することに関心が集まっています。規格ではさまざまなテストが要求されているため、設計や検証を担当するエンジニアは、迅速かつ確実に実施できるテスト・ツールを使用し、効率アップを図ることが必要になります。

本アプリケーション・ノートでは、検証テストと、複雑なHDMI信号をテストする際に直面する課題について紹介するとともに、広範囲なテスト(シンク・テストを含む)を自動化し、信頼性の高い測定結果により、これまでにない優れた効率アップを実現するオシロスコープ内蔵型アプリケーション・ソフトウェアについて説明します。

基礎

HDMIでは、TMDS(Transition Minimized DifferentialSignaling)技術を活用します。差動信号の電圧は+3.3V、終端は50Ω、公称の振幅電圧は500mV(+2.8V~+3.3V)です。電圧スイングは、150mV~800mVの範囲で変動します。信号の立上り時間は100ps台です。

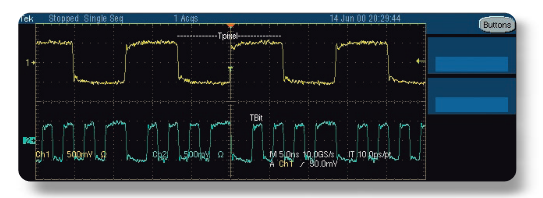

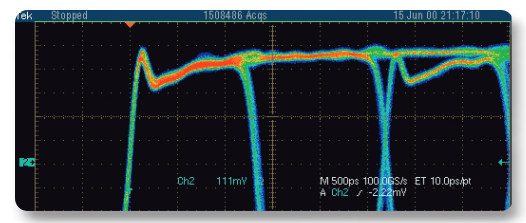

1つのリンクのデータ・レートは、25Mpps~165Mppsです (Mpps =メガピクセル/秒)。1ピクセルは10ビットのデータで 表されるため、ビット時間(一般的にTBITで表される)は、最短 で606psにもなります。図1は、一般的なHDMIデータ信号で す。ほとんどの制限値はTBIT、つまり、データ信号のビット時間 を基準にして規定されています。

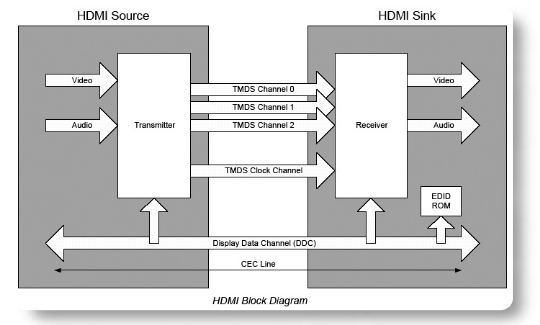

TMDS伝送リンクは、3つのデータ・チャンネルと1つのクロック・チャンネルで構成されます。TMDSリンクを2つ使用して、最大330Mppsのデータ・レートを得ることができます。図2は、TMDS信号伝送のリンクの概念図です。

HDMI物理層コンプライアンス規格

信頼性の高い情報伝送とインターオペラビリティ(相互接続性) を保証するため、規格では、ネットワーク物理層の要件を規定し ています。HDMIスペシフィケーション[1]、具体的にはHDMI CTS(コンプライアンス・テスト・スペシフィケーション)[2] では、HDMI物理層に関する広範なコンプライアンス・テストに ついて規定しています。

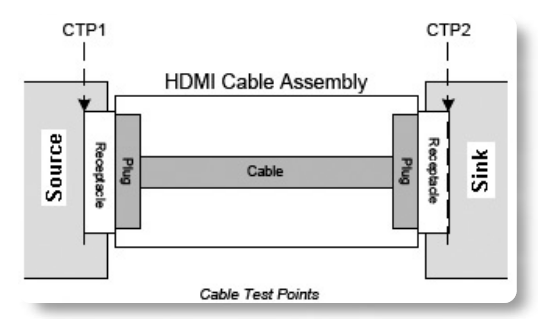

図3は、HDMI伝送システムの主な構成要素であるソース、ケー ブル、シンクを示しています。ソース信号はTP1で測定し、一 方、シンク機器はTP2でテストして、それぞれが規格の制限値 内にあるかどうかを確認します。また、ケーブルのテストでは、 TP1、TP2の両方で測定を実施する必要があります。まずTP1 で測定を行い、TP2における測定が既知の環境で実施されるよ うにします。

できるだけ多くのテストを実施すべきですが、コンプライアンスにおいて特に重要なのがコア・テストです。下の表では、コア・テストの一部について要約しています。

| Electrical | Signals | Test | CTS Test ID | Test Point |

| Source | Clock and/or Data | Data Eye Diagram Clock Jitter Clock Duty Cycle Overshoot/Undershoot Rise/Fall Time Inter-pair Skew |

7-10 7-9 7-8 7-5 7-4 7-6 |

TP1 TP1 TP1 TP1 TP1 TP1 |

| Data-Data | Inter-pair Skew | 7-6 | TP1 | |

| Single-ended | Intra-pair Skew Low Level Output Voltage (VL) |

7-7 | TP1 | |

| Sink | Jitter Tolerance Minimum Differential Sensitivity Intra-pair Skew Differential Impedance |

8-7 8-5 8-6 8-8 |

TP2 TP2 TP2 TP2 |

|

| Cable | Data Eye Diagram | 5-3 | TP1, TP2 |

ソース機器電気特性テスト

このテストは、TP1においてクロック信号やデータ信号に対し て実施します。ソース電気テストは、セットアップによって、さ らにクロック-データ、データ-データ、シングルエンドのテスト に分類されます。これらのテストについては、以降のセクション で詳しく説明します。

1. クロック-データ・テスト

a. データ・アイ・ダイアグラム・テスト

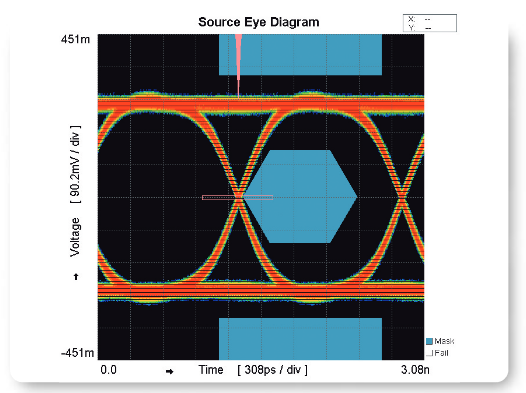

このテストの目的は、差動データの「アイが十分に開いて」いて、 伝送先のシンク機器において有効な再生を行えるかを確認するこ とです。データは、再生クロックによりクロッキングされ、 +1.0TBITのウィンドウ・サイズで表示されます。マスクとの比較 によって合否を判定し、データ・ジッタを解析することで、シグ ナル・インテグリティに関する重要な情報が得られます。

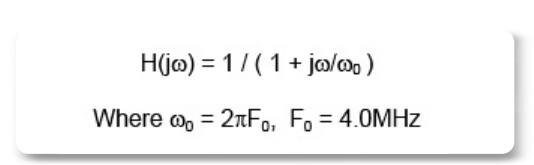

CTSでは、クロック・リカバリの方法について明確に規定しています。クロック・リカバリには、図4のPLL関数を使用します。

信号の特性を十分に表すため、CTSでは、オシロスコープでデ ータ信号を捕捉する際の最低レコード長についても規定していま す。これにより、アイ・ダイアグラムの作成時には、最低でも 400,000ユニット・インターバル(またはTBIT)が必要となり ます。レコード長が16Mポイントあれば、低表示分解能の信号 では400,000UI、高表示分解能の機器では2.6M UI以上を取り 込むことができます。

図5*は、オシロスコープで実施したアイ・ダイアグラム・テス トの表示例です。マスクは、違反が起こるまで左にシフトさせま す。このテスト法では、正確なスライス技術が要求されます。ま た、制限値が厳しいため、違反検出も厳しい条件のもとで行う必 要があります。一般に、オシロスコープ画面は500×400ピク セル以上の分解能があり、スクリーン・イメージでのマスク・ヒ ットに基づいて、合否テストを行います。

この方法はHDMIの分解能が低い場合には十分な結果が得られますが、分解能が高くなると不正確な結果が多くなります。このような場合は、実際のデータ・サンプル分解能までフォーカスして、マスク違反テストを実施してみるのがよいでしょう。スクリーンの分解能では、正しい結果は得られません。

b. クロック・ジッタ

伝送システムの中枢として機能するのがクロック信号です。ジッタ・テストでは、クロック信号に過剰なジッタが含まれていないかを確認します。このテストを実施する場合、クロックは再生クロックを基準にします。規格で定めているクロック再生関数は、前記の図4と同じです。

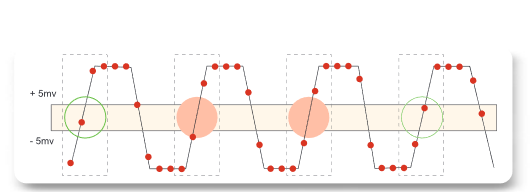

クロック信号は、再生クロックを基準にしてプロットします。ヒストグラム・ボックスをエッジの中央に置き、信号のスパンによってその信号に存在するジッタの量を判断します。規格適合に必要なジッタの測定値は、0.25TBIT未満です。

従来、ヒストグラム・ボックスを使用してジッタを測定する場合、ボックスを立上りエッジの中央に置き、高さを最小限に抑えるという手法がとられてきました。この技術を便宜上、「最小ボックス・アプローチ」と呼ぶことにします。

ただし、165MHz前後のクロック・レートとなると、エッジのサンプル数はそれほど多くありません。サンプルが少ないという問題を克服するために、ヒストグラム・ボックスのサイズを縦方向に拡大することもできますが、このようにすると、実質的に「最小ボックス・アプローチ」ではなくなります。そのため、図6のようにジッタ値が高くなります。

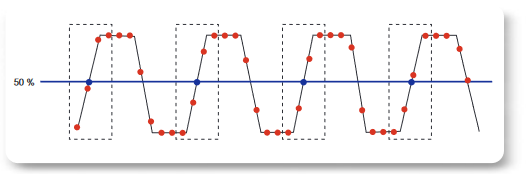

「最小ボックス・アプローチ」とサンプル補間を併用して測定することで、ジッタについて詳しく把握することができます。図7は、補間したサンプルを使用した、「最小ボックス・アプローチ」によるジッタ測定を示しています。この値を図6と比べると、「最小ボックス・アプローチ」による補間の効果が明らかです。

TIE (Time Interval Error)も、ジッタ評価に有効な技術です。この方法では、サイクルごとにエッジのずれを求め、最小と最大の差をピーク間のジッタとして表します。この場合も、補間で分解能を上げることで、解析やテストを正確に行うことができます。

c. クロック・デューティ・サイクル

デューティ・サイクル・ジッタは、周期性ジッタを評価する優れた方法です。CTSでは、デューティ・サイクルの制限値を、公称50%の+10%と規定しています。したがって、TDUTYの測定値が40~60%の範囲に収まるようにします。

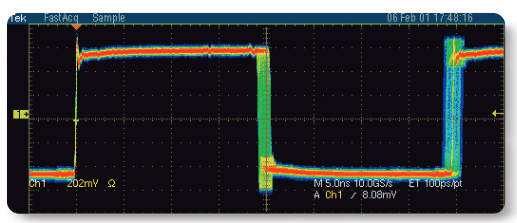

デューティ・サイクルの変動は、波形を多数捕捉し、測定することが重要です。CTSによれば、テストの目的では最低でも10,000波形が必要です。そこで、オシロスコープのトリガ・リアーム・レートが問題になります。一般に、オシロスコープのトリガ・リアーム・レートは、毎秒100波形(wfms/s)程度とされています。これでは、波形の捕捉やテストに膨大な時間がかかってしまいます。

しかし、デジタル・フォスファ・オシロスコープ(DPO)のFastAcqアクイジション・モードのような高度な技術を使用すれば、トリガ・リアーム・レートを高め、毎秒400,000波形以上の捕捉が可能です。図8は、FastAcqモードを使用したクロック・デューティ・サイクルのテストを示しています。測定値の信頼性を高めるための、豊富な情報が得られることがわかります。

d. オーバシュート/アンダシュート

オーバシュート/アンダシュート・テストでは、信号が規定の制限値内にあるかを確認します。トランスミッタがチャンネルをオーバドライブし、EOSが発生したり、干渉が起きたりしないかを確認します。また、信号の再生性のテストによって、インターオペラビリティ(相互接続性)も確認します。

CTSでは、オーバシュートを、安定状態での電圧スイング全体の15%以内、アンダシュートを25%以内と規定しています。テストは、クロックおよびデータ・ペアに対して実施します。テストでは、立上り/立下りエッジの両方について、電圧スイング(VHVL)と、オーバシュート/アンダシュートの正確な値を含む複数のパラメータを測定する必要があります。1回のテストで結果を得るには、6つ以上のパラメータの測定が必要です。

多数のパラメータを測定するだけでなく、信頼できる方法で測定することも非常に重要です。オーバドライブを起こすことなく、できるだけ広いA/Dレンジを使用するには、表示される信号のサイズをできるだけ大きくする必要があります。図9は、正確なオーバシュート測定例です。制限値が厳しいため、信頼性の高い測定結果を得るには、このような慎重な測定が必要になります。

e. 立上り/立下り時間

立上り/立下り時間は、ほとんどの物理層テストで主要なテスト項目になっています。制限値に対して、必要な信号速度が得られているか、また、EMIが含まれていないかを確認します。CTSでは、立上り/立下り時間を75psより大きく、0.4TBIT未満と規定しています。

クロック・デューティ・サイクル・テストの場合と同様、このテストでも多数の波形を捕捉する必要があります。ここでも、トリガ・リアーム・レートが重要になります。DPOのFastAcqモードを使用すれば、このテストを簡単に実施できます。

f. クロック-データのインターペア・スキュー

インターペア・スキューは、インターオペラビリティ(相互接続性)を確認する上できわめて重要なテストです。このテストでは、クロックとデータ・ペアとのスキューが制限値内にあることを確認します。CTSでは、スキューはピクセル時間(TPIXEL)の20%を超えてはならないと規定しています。インターペア・スキューのテストは、データ・チャンネル間でも実施します。このテストについては、次の「データ-データのテスト」のセクションで詳しく説明します。

2. データ-データのテスト(インターペア・スキュー)

インターペア・スキュー・テストにおいては、重要な検討事項が いくつかあります。第1に、実質的にスキューを測定できるのは、 両方のデータ・ペアが特定のパターンを伝送している場合に限ら れます。第2に、測定経路(プローブを含むオシロスコープの測 定システム)が起因したスキューを発生させる可能性があります。 第3に、オシロスコープは、特定のシリアル・パターンでトリガ する必要があります。これは、シリアル・トリガ機能とも呼ばれ ます。そして最後に、制限値はピクセル時間を基準にして規定さ れています。そのため、クロック・レートを正確に測定すること も重要になります。

測定経路のスキューをなくすことは重要です。このプロセスは、デスキュー・プロセスと呼ばれています。正確な結果を得るためには、テストの前にデスキューを実施します。

3. シングルエンドのテスト

このテストは、シングルエンド・プローブを使用してペアごとに実施します。

a. イントラペア・スキュー

イントラペア・スキュー・テストは、差動信号において、さまざ まな信号伝送の影響を明らかにするために実施します。規格では、 差動ペア内でテストした場合のスキューは、ビット時間(TBIT) の15%以内と規定されています。インターペア・スキューの場 合と同様、テストの前にデスキューを実施することが重要です。 これにより、プロービングや測定システムのスキューが原因のエ ラーが最小限に抑えられます。

b. ロー・レベル出力電圧(VL)

VLテストは、信号電圧レベルが規定の制限値内にあるかを確認します。HDMIリンクでのDC電圧レベルを、TMDS信号にて確認します。CTSでは、低レベル電圧の範囲を2.7~2.9Vと規定しています。

適合試験には、多くの捕捉波形が必要です。規格では、最低10,000波形が必要です。FastAcqを使用すれば、このテストを迅速に行えます。電圧レベルの測定には、ヒストグラム法を使用します。ヒストグラムの統計最高値(ヒストグラム・ピーク)をVLで表し、規格の制限値と比較します。

ソース・テストの準備

a. 必要機器

以下の表は、これまでに説明したテストを実施するために必要な機器についてまとめています。

CTSが定めているこの他のテストでは、さらにデジタル・マルチメータ、プロトコル・アナライザ、LCRメータ、I2Cアナライザなどが必要になります。

b. テスト機器の選択にあたり注意すべきこと

テストのセットアップに適した機器を選ぶと同時に、対処すべき点について理解しておくことが大切です。いくつかの点について説明します。

デジタル・ストレージ・オシロスコープ

測定精度は、測定システムの性能に依存します。HDMI信号の立上り時間について検討すると同時に、必要な周波数帯域を選択することが重要です。対応している表示分解能、リフレッシュ・レート、ブランキング期間などを使った簡単な計算で、TBIT値の有効な指標を得ることが可能です。また、T BIT値を使用して、HDMI信号のおおよその立上り時間(0.2~0.3TBIT)を求めることもできます。

クロック・レートが165MHzであれば、立上り時間は75~250psになると考えられます。例えば、テクトロニクスのTDS7704B型では、60ps台の立上り時間が得られるため、立上り時間が180psを超える信号に対して有効です。

アイ・ダイアグラムおよびクロック・ジッタのテストでは、最低でも16Mポイントのレコード長が必要です。アイ・ダイアグラム・テストは、2つのチャンネル(データおよびクロック)を使用するため、チャンネルごとに16Mポイントが必要です。

多数の捕捉波形(10,000波形以上)を必要とするテストがいくつもあるため、テストを迅速化するには、高速のトリガ・リアーム・レートが必要です。テクトロニクスは、テストを迅速化するFastAcqモードを備えたオシロスコープを数多く取り揃えています。

インターペア・スキュー・テストでは、特定のシリアル・パターンでのトリガが必要です。このテストを実施する上で、シリアル・トリガ機能は不可欠です。

| Test | Digital Oscilloscope | Differential Probes | Single-ended Probes | TPA-P Test Adapter Set | DC Power DC Power | EDID Emulator |

| Eye Diagram | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Clock Jitter | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Duty Cycle | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Over/Undershoot | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Rise/Fall Time | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Inter-pair Skew | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Intra-pair Skew | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Output Low VL | ⬤ | ⬤ | ⬤ | ⬤ | ⬤ | |

| Notes | 16 M RL, ST | > 2 nos. | 2 nos. | 1 set | 3.3 V | From SI |

差動プローブ

HDMI TMDS信号伝送では、差動伝送方式を使用します。同相 除去比、感度、応答特性が高く、ノイズ・フロアが低い差動プロ ーブが、この目的に適しています。信号伝送レートが高く、制限 値も厳しいため、プロービングのさまざまな側面や選択肢につい て理解しておくことが非常に重要です。入門書『高速差動データ 信号伝送と測定』(3)では、これらについて説明しています。

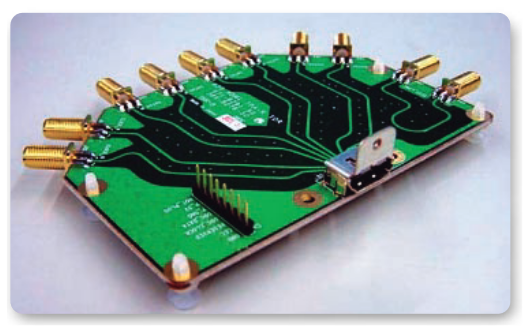

差動プローブは同一の入力ピンを2個備えているため、信頼性の高 い接続がより困難になります。スクエア・ピンを備えたテスト・ア ダプタへの接続は、慎重に検討する必要があります。プローブ・チ ップ・アダプタは多様な選択肢がありますが、アプリケーションに 合わせて、それらの選択肢を十分に吟味する必要があります。例え ば、テクトロニクスのP7350SMA型プローブ2本をTPA-P-TDR 型アダプタで接続すると、SMAによる接続で信頼性の高い結果を 得ることができます。

テクトロニクスの入門書では、それぞれの選択肢について詳細に 説明しています。例えば、バリアブル・スペーシング・アダプタ を使用すると、オーバシュートが大きくなる可能性があります。 面倒でも、テスト・ポイントへ半田付けすることで、最善の結果 が得られます。テクトロニクスのP7380型プローブはさまざま なチップが利用でき、半田付け、プロービング・アームによるプ ローブの固定、あるいは、ハンドヘルド型のハウジングにより、 測定点への直接のプロービングも可能です。

プローブの周波数帯域も重要な検討事項です。この場合も、信号の立上り時間に応じて、信号忠実性を確保するのに十分な速さの立上り時間が得られるプローブを選択する必要があります。テクトロニクスのオシロスコープとプローブは、プローブの先端で必要なシステム周波数帯域を提供します。

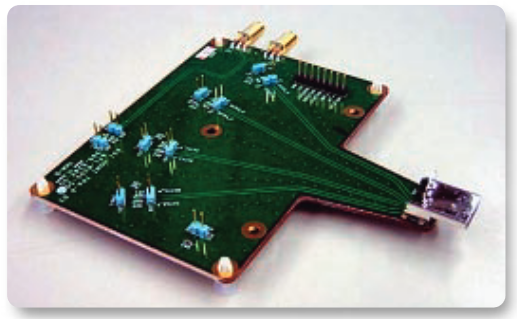

テスト・アダプタ

確実な接続を行うことが、精度やシグナル・インテグリティを維 持する鍵になります。テスト・アダプタ・セットには、2つのタ イプがあります。ほとんどのソース機器の場合、DUT(被テス ト機器)への一次接続には、プラグ・タイプのアダプタ(TPAP)が適しています。図10は、TPA-Pプラグ・タイプのテス ト・アダプタです。

自動テスト・ツール

ソース・テストによって規格適合を証明するには、さまざまなテストを信頼できる方法で実施することが必要になります。これらのテストは、制限値が厳しく手順も複雑なため、非常に多くの時間がかかります。また、大部分のテストは、最適の条件で実施する必要があり、ユーザはHDMI技術やテスト機器の使用に精通していなければなりません。いずれにしても大変な課題です。

しかし、本書で後述するHDMIコンプライアンス・テスト・ソフトウェア TDSHT3を使用すれば、迅速かつ信頼性の高いテストが可能になります。確かな測定技術は、測定結果の信頼性を高め、自動化によって、テスト・プロセスを実施するユーザの負担が軽減されます。

c. ソース・テストのセットアップ

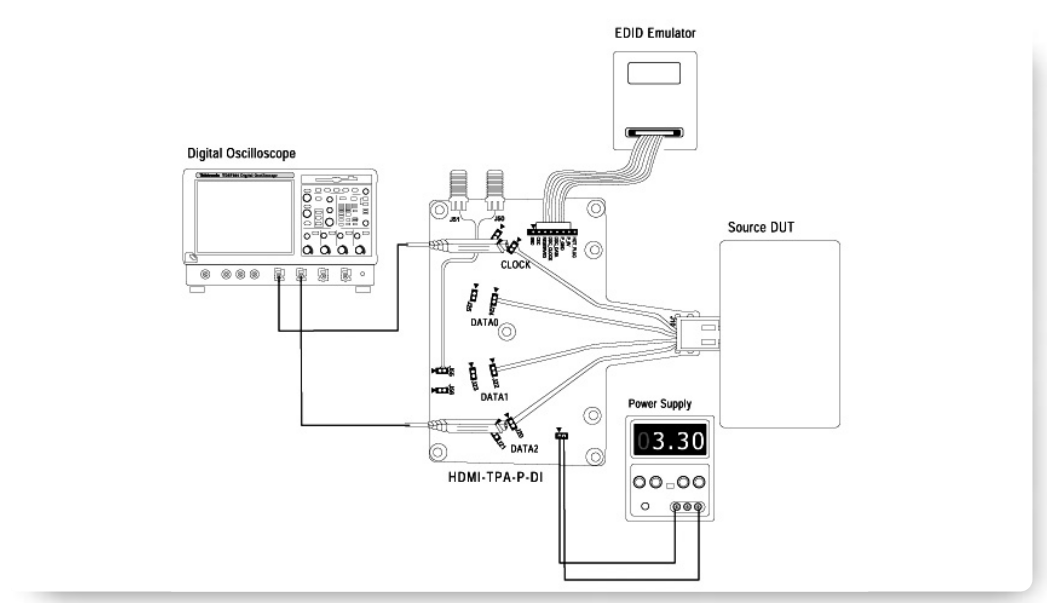

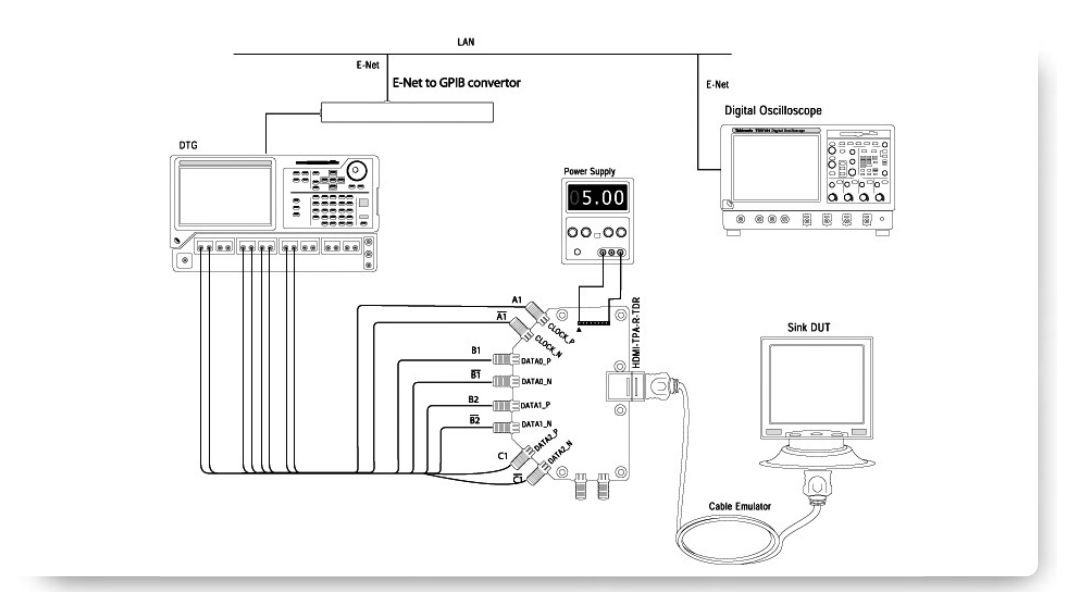

クロック-データおよびデータ-データのテストについては、図11を参照してください。

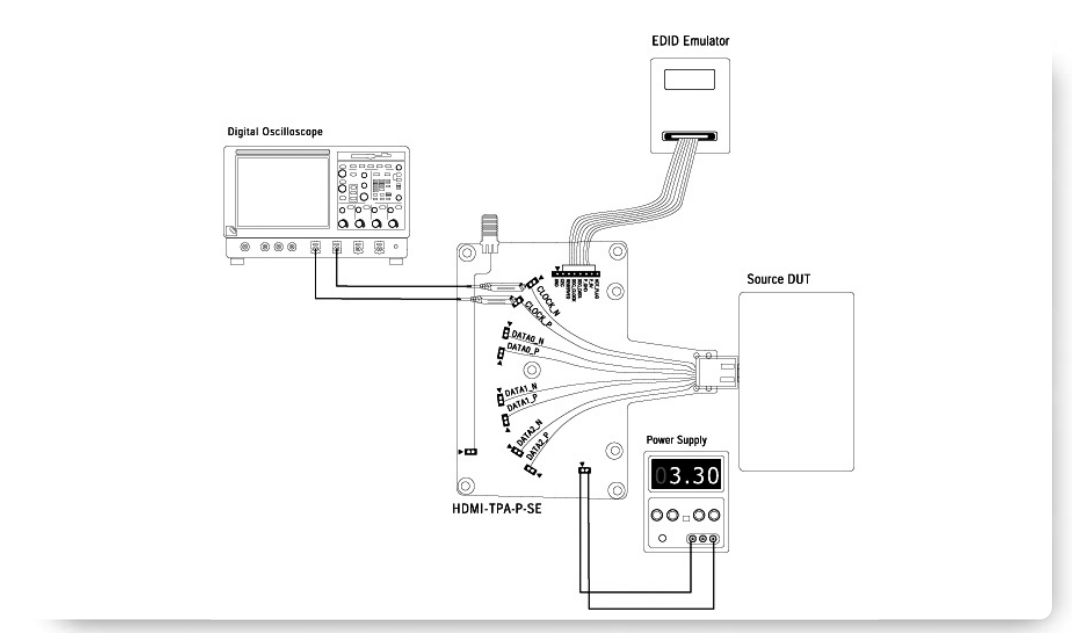

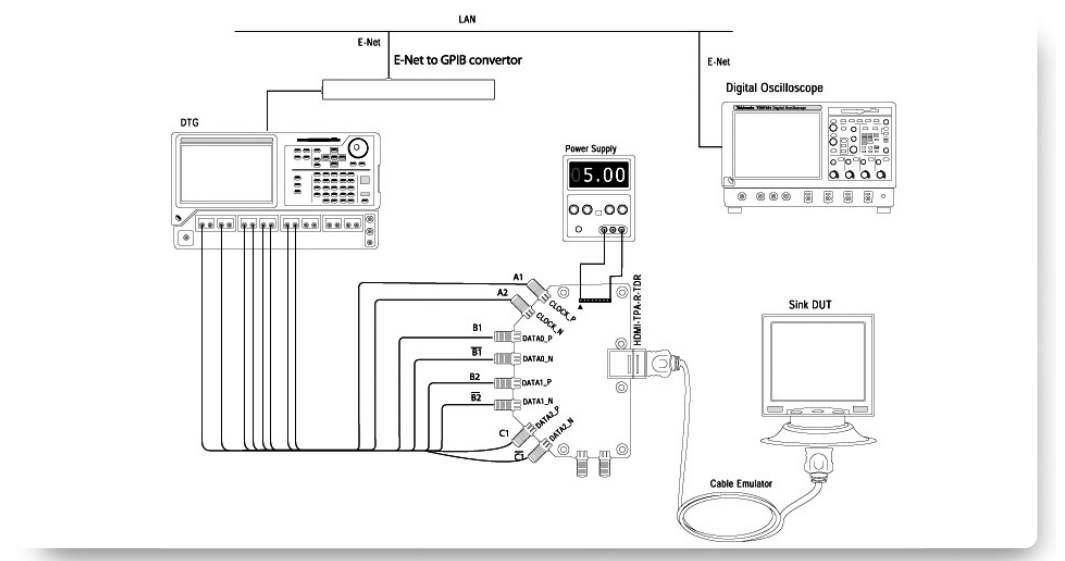

シングルエンドのテストについては、図12を参照してください。

d. DUTからのテスト信号の取得

- EDIDエミュレータの設定:シンク機器とのEDIDハンドシェーク動作をエミュレートします。PCベースのソフトウェアを使用して、EDIDエミュレータへ必要な分解能に設定します。

- 外部電源の供給:プルアップ抵抗で電圧を引き上げられるようにします。

- 必要なテスト・パターンが規定されているわけではないため、ソース機器で作成したHDMIパターンであれば、どのようなものでもかまいません。例えば、DVDプレーヤでDVDを再生しても、必要なテスト信号は得られます。

接続の詳細については、前述のテスト・セットアップを参照してください。

シンク機器電気特性テスト

これらのテストは、シンク機器側のHDMIコネクタ、TP2で実施します。これらのテストについて、以降のセクションで詳しく説明します。

1. ジッタ・トレランス・テスト

シンク機器において最も重要な特性の1つは、信号に含まれる一定レベルのジッタに対するトレランスです。規格では、この限界値を0.3TBITと規定しています。

伝送したTMDS信号に対し、シンク機器がその信号を再生できなくなるまで、ジッタを一定量ずつ増加させます。そして、そのシンク機器が許容できるジッタの量を、コンプライアンスで求められる限界値と比較します。

ジッタ・トレランス・テストの大まかな手順を以下に示します。

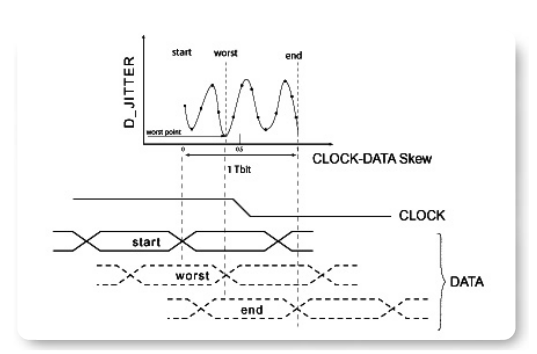

- ワースト・ケース・クロック-データ・スキューの決定:データのスキューを変えながら、最悪になるポイントを決めます。このテストは、図13のように何度も繰り返して実施します。その後、この最悪のスキューが発生するようにTMDSシグナル・ゼネレータを設定します。

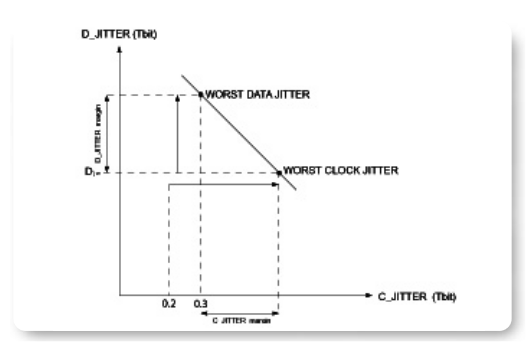

- ジッタ・マージンの測定:一定量のジッタを注入しながら、数種類の測定を実施します。次のような2通りのテスト・ケースで3種類の測定を実施します。(a)データ・ジッタ周波数が500KHz、クロック・ジッタ周波数が10MHz。(b)データ・ジッタ周波数が1MHz、クロック・ジッタ周波数が7MHz。3種類の測定は以下の通りです。

- データ・ジッタ振幅(Djw)

- ワースト・データ・ジッタ振幅

- ワースト・クロック・ジッタ振幅

図14は、D_ JITTERおよびC_ JITTERの値の測定基準をわかりやすく示しています。

このテストは、シンク機器が対応しているすべてのピクセル・クロック・レートで実施する必要があります。さまざまなパラメータの調節が必要で、しかも制限値が厳しいため、非常に複雑で時間のかかるテストになりがちです。

2. 最小差動感度

これは、ほとんどのシリアル規格で広く実施されているテストです。このテストでは、差動電圧スイングが減衰した状態でも、シンクがインターオペラビリティ(相互接続性)を適切に保持できるかを確認します。

このテストでは、振幅の変更が可能なTMDSシグナル・ゼネレータを使用します。そして、シンク対応の27MHzのビデオ・フォーマットを作成し、ビデオ期間ごとに255階調のRGB信号を繰り返し発生させます。

テストは、各ペアで170mV VDIFFから始め、シンク機器がエラーをレポートするまで差動スイングを20mVずつ減少させます。シンク機器がエラーなく対応した最小VDIFFが150mV未満であれば、この機器は合格です。テストは、最小VDIFFが70mVに達した時点で終了します。

このテストでは、3.0Vおよび3.13Vという2通りのVICM(同相電圧)設定で実施するという点も重要です。

3. イントラペア・スキュー

シンク機器には、イントラペア・スキューに対するトレランスも必要です。このテストでは、シンク機器が、各TMDSペア内のタイミング・スキューに対応できるかを確認します。CTSでは、イントラペア・スキューに対するトレランスの制限値を0.4TBITと規定しています。

このテストでは、まずクロックとデータ・ペアをスキューのない状態に設定し、シンク機器がエラーを出力するまで、各ペア内のスキューを0.1TBITずつ(1度に1ペアずつ)増加させます。エラーのない状態でシンク機器を操作できるスキューの最大値をペア内スキューとし、規格の制限値と比較します。0.4TBITを上回れば、その機器は規格に適合しています。

4. 差動インピーダンス

高速のデータ・レートを得るために使用する差動伝送回線は、イ ンピーダンスが整合しているかどうかによって大きく影響を受け ます。そのため、インピーダンスの測定は、HDMIのコンプライ アンス・テストの中でも非常に重要です。接続全体のインピーダ ンスにおける変動は、規定の100Ωに対して15%以内とされて いますが、終端部分のインピーダンスは10%以内と、非常に厳 しくなっています。

このテストは、シンク機器のスイッチを切った状態で実施します。まず、入力コネクタまでの測定距離を測定します。TDRを使用して測定するのが最もよい方法で、インピーダンス曲線が200Ωより上に急上昇するポイントを特定し、コネクタまでの距離を求めることができます。

続いて、入力コネクタから、インピーダンス曲線が安定して終端インピーダンスになる地点までの差動インピーダンス値ZDIFFをペアごとに測定します。テストをしないペアは、50Ωで終端します。ZDIFF値が85~115Ωの場合、その機器は合格です。

TDRテストや制御インピーダンスの測定について理解を深めるため、テクトロニクスでは詳細に説明したアプリケーション・ノートを用意しています(参考文献4と5を参照)。

| Jitter Tolerance | Min. Diff. Sensitivity | Intra-pair Skew | Differential Impedance | Remarks | |

| Digital Storage Oscilloscope | ⬤ | ⬤ | ⬤ | 16M RL | |

| Differential Probes | ⬤ | ⬤ | ⬤ | > 2 nos. | |

| Data Timing Generator | ⬤ | ⬤ | ⬤ | DTG5274 with 3 DTGM30 | |

| Arbitrary Waveform Generator | ⬤ | AWG710/B | |||

| TDR Sampling Oscilloscope | ⬤ | TDS8200 with 80E04 + 80E03 | |||

| TPA-R Test Adapter Set | ⬤ | ⬤ | ⬤ | 013-A012-50 | |

| TPA-P Test Adapter Set | ⬤ | ⬤ | ⬤ | ⬤ | 013-A013-50 |

| 50 Ω terminations (6 nos.) | ⬤ | 015-1022-01 | |||

| SMA-BNC adaptor | ⬤ | 015-1018-00 | |||

| Cable from DTG DC O/P Pin-to-SMA at Bias Tee (2 nos.) | ⬤ | 012-1506-00 + 015-0671-00 + 015-1018-00 | |||

| SMA Cables (12 nos.) | ⬤ | ⬤ | ⬤ | 174-1428-00 | |

| SMA(m) – SMA(f) Cables (2) | ⬤ | *1 below | |||

| Mini-Circuits Bias Tee (2 nos. | ⬤ | ZFBT-4R2GW *1 | |||

| JAE Cable Emulator (1 each) | ⬤ | 74.25, 27 MHz | |||

| DC Power Supply | ⬤ | ⬤ | ⬤ | ⬤ | +5V |

| GPIB USB Controller | ⬤ | ⬤ | ⬤ | ⬤ | NI GPIB-USB-B |

| GPIB Cable | ⬤ | ⬤ | ⬤ | ⬤ |

1: Preferable to have SMA (m) at RFin and SMA (f) at RF+DC output port.

シンク・テストの準備

a. 必要機器

下の表は、これまでに説明したシンク・テストを実施する上で必要な機器についてまとめています。

CTSが定めているこの他のテストでは、さらにデジタル・マルチメータ、プロトコル・アナライザ、LCRメータなどが必要になります。

b. テスト機器の選択にあたり注意すべきこと

テストのセットアップに適した機器を選ぶと同時に、対処すべき点について理解しておくことが大切です。いくつかの点について説明します。

デジタル・ストレージ・オシロスコープ

ジッタ・トレランスのテストでは、オシロスコープに最低でも16Mポイントのレコード長が必要です。

データ・タイミング・ゼネレータ

シンク・テストで中心的な役割を果たすのがTMDSシグナル・ゼネレータです。TMDSシグナル・ゼネレータの使用において最も重要な点は、精度の高い信号が出力できることと、パラメータを正確に調整できることです。

最小差動感度テストを実施する場合は、20mVの分解能が必要です。イントラペア・スキューのテストでは、遅延をピコ秒以下の分解能で厳密に設定する必要があります。テクトロニクスのDTG5274型(+DTGM30型モジュール)は、データ・ゼネレータとパルス・ゼネレータの機能を組み合わせ、非常に正確なテスト信号によるシンク・テストを可能にします。

任意波形ゼネレータ

ジッタ・トレランスのテストは、クロック・ジッタとデータ・ジ ッタをさまざまに変化させる必要があるため、それだけ課題も多 くなると考えられます。10MHz程度のジッタ周波数を発生させ るには、シグナル・ゼネレータを組み合わせる必要があります。 制限値が厳しいため、ジッタ振幅を厳密に制御する必要がありま す。テクトロニクスのAWG710B型は、このような要求を満た す最適なプラットフォームです。

TDRサンプリング・オシロスコープ

TDR(Time Domain Reflectometry)は、相互接続における インピーダンスや長さを測定するための、正確で効果的な方法で す。TDRの基本概念は比較的単純ですが、正確な測定を行うに は、さまざまな問題に対処する必要があります。その中で最も重 要なのは、真の差動TDRを実施できるかどうかということです。 そのため、TDS8200型本体と80E04型モジュールの組み合わ せが、差動インピーダンス・テストを実施する上で、最善の選択肢になります。TDRで回路基板をプロービングする場合は、 P8018型プローブを80A02型モジュールに接続して使用しま す。

ケーブルを(製造などにおいて)テストする場合は、80A02型モジュールにフット・ペダル・アクチュエータを組み合わせるだけでよく、P8018型プローブは必要ありません。これにより、ケーブル接続時の誤操作が防げます。

テスト・アダプタ

ソース・テストの場合と同様、確実な接続を行うことが、シン ク・テストにおいて精度やシグナル・インテグリティを維持する 鍵になります。テスト・アダプタ・セットには、2つのタイプが あります。ほとんどのシンク機器の場合、DUT(被テスト機器) への一次接続には、プラグ・タイプのアダプタ(TPA-P)セッ ト、およびレセプタクル・タイプのアダプタ(TPA-R)が適し ています。図15は、TPA-Rレセプタクル・タイプのアダプタで す。

自動テスト・ツール

ソース・テストの場合と同様、シンク・テストも多大な時間を要します。シンク・テストでは、測定において複数の機器を制御しなければならない上、ジッタ・パラメータを厳密に設定する必要があるため、一層複雑になります。そのため、自動化がおのずと必要になります。

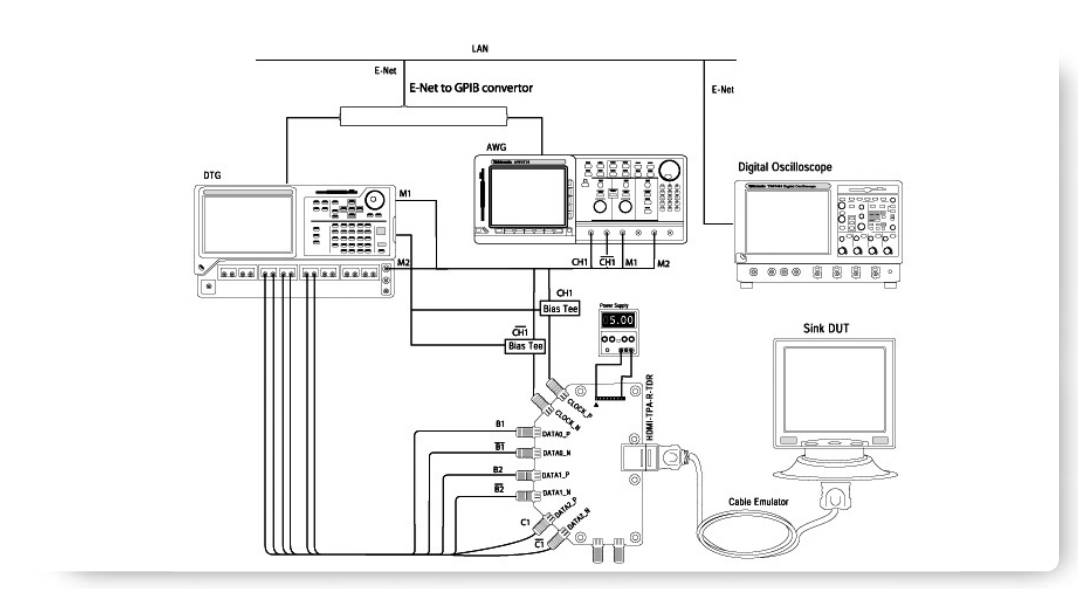

本書で後述するHDMIコンプライアンス・テスト・ソフトウェア TDSHT3を使用すれば、テスト・プロセス全体を簡素化し、 GPIBを使用してさまざまなパラメータをリモート制御できま す。TDS7000BシリーズDPOをGPIBコントローラとして動作 させ、イーサネット・コントローラまたはGPIB-USBコントロ ー ラ ( 共 に National Instruments社 製 )を使用し、 DTG5274型、AWGをGPIBで制御します。

c. シンク・テストのセットアップ

ジッタ・トレランス・テスト(図16を参照)

最小差動感度(図17を参照)

イントラペア・スキュー(図18を参照)

ケーブル電気テスト

ケーブル電気テストは、HDMIケーブルのTP1、TP2の両ポイントで実施します。これらのテストについて、以降のセクションで詳しく説明します。

1. データ・アイ・ダイアグラムのテスト

このテストの目的は、ケーブルによって、信号がソースからシンクへ正しく中継されるかを確認することです。

ケーブルによって、信号にある程度の劣化が予想されます。その劣化が、機器間のインターオペラビリティ(相互接続性)に影響を及ぼさない程度の低いものであるかをテストで確認します。

ケーブルを伝送システムに取り付ける前に、まずTP1で信号を 測定します。TMDS信号は、HDMIシグナル・ゼネレータで発生 させます。HDMIシグナル・ゼネレータのパラメータを調整して、 伝送する信号に一定量のクロック・ジッタとデータ・ジッタが含 まれるようにします。アイ・ダイアグラムとジッタで、このテス ト条件が満たされていることを確認してから、ソースの場合と同 様の方法でテストします。

続いてケーブルを接続し、今度はTP2でアイ・ダイアグラムを検証します。規格では、複数の条件下でテストした場合のTP2における劣化の量について、明確に規定しています。

- マスク・テスト

- データ・ジッタ0.67ns以下(75MHzで、0.5TBITに相当)

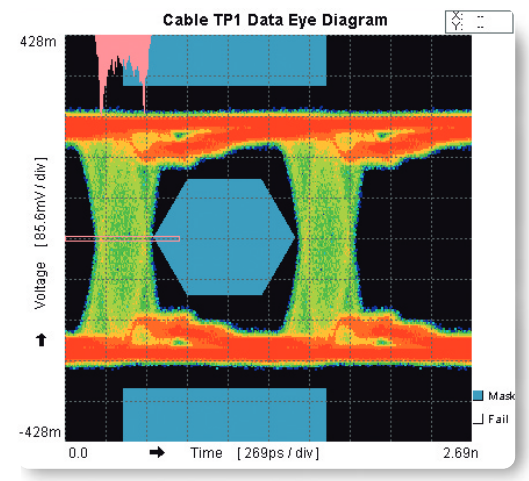

データ・ジッタの測定には、ヒストグラム・ボックスを使用しま す。ソースのジッタ・テストの場合と同様、最小ボックス・アプ ローチを使用すると、ジッタについて詳しく知ることができます。 最小ボックス・アプローチでデータ・ジッタを測定すると、信頼 性の高い結果が得られます。図19(TP1)、図20(TP2)は、 オシロスコープでのケーブルのアイ・ダイアグラム・テストの様 子を示しています。

2. オプショナル・パラメータ・テスト

ケーブルのシグナル・インテグリティの指標として非常に有効なテストです。以下のテストを実施するよう推奨しますが、必須ではありません。

- イントラペア・スキュー

- インターペア・スキュー

- 遠端クロストーク

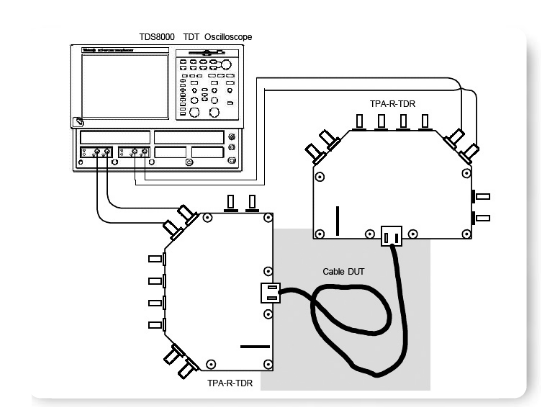

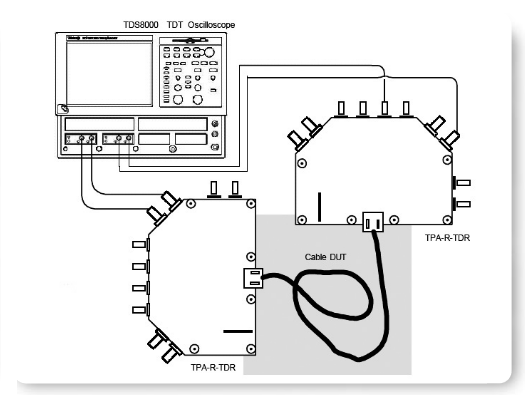

イントラペア・スキューおよびインターペア・スキュー・テスト は、サンプリング・オシロスコープを使用して実施します。これ らのテストには、シンクの差動インピーダンス・テストの項で紹 介した、テクトロニクスTDS8200型に、TDTプラグインを組 み合わせて使用することができます。また、2チャンネルのサン プリング・モジュールで、各チャンネルにTDRステップ・ゼネ レータを備えたテクトロニクス80E04型も、このテストに使用 することができます。遠端クロストークのテストには、ネットワ ーク・アナライザを使用するのが普通ですが、クロストーク測定 にTDRを使用すれば、迅速かつ直感的な測定ができ、コストも 低減できるというメリットがあります。TDRによるクロストー クの測定については、TDA Systems社のアプリケーション・ ノートが役に立ちます。

ケーブル・テストの準備

a. 必要機器

下の表は、これまでに説明したケーブル・テストを実施する上で必要な機器についてまとめています。

また、ネットワーク・アナライザを使用することで、遠端クロストークのテストを実施できます。

b. テスト機器の選択にあたり注意すべきこと

テストのセットアップに適した機器を選ぶと同時に、対処すべき点について理解しておくことが大切です。いくつかの点について説明します。

デジタル・ストレージ・オシロスコープ

規格への適合を確認するには、最低でも16Mポイントのレコー ド長が必要です。データ・ジッタを測定する必要があります。ま た、ソース・テストの場合と同様に、ジッタはPLL再生クロック を基準にして測定するという点も重要です。前述のように、信頼 できるデータ・ジッタ測定値を得るには、最小ボックス・アプロ ーチが最適です。

データ・タイミング・ゼネレータ

ケーブル・テストで中心的な役割を果たすのがTMDSシグナル・ゼネレータです。テクトロニクスのDTG5274型(+DTGM30型モジュール)は、データ・ゼネレータとパルス・ゼネレータの機能を組み合わせ、精度の高いテスト信号によるケーブル・テストを可能にします。

サンプリング・オシロスコープ

スキュー・テストの制限値に対応するには、極めて高精度の測定が必要です。TDS8200型本体と80E04型または80E03型モジュールを組み合わせることで、このテストに必要な測定精度や分解能が得られます。

自動テスト・ツール

ケーブルのデータ・アイ・ダイアグラムのテストには、ソース・ テストおよびシンク・テストの両方の複雑さを伴います。複雑な アイ・レンダリング、データ・ジッタの正確な測定技術、そして いくつもの機器を制御しなければならず、このテストは非常に複 雑なものになります。本書で後述するTDSHT3は、こうしたテ ストの負担を軽減します。TDS7000BシリーズDPOは、イー サネット・コントローラまたはGPIB-USBコントローラで DTG5274型と接続します。

台湾のLiTek社は、これ以外のさまざまなテストを自動化する高速ケーブル・テスト・ソリューション(LT-4165)を提供しています。

| Data Eye Diagram | Intra-pair Skew | Inter-pair Skew | Far End Crosstalk | Remarks | |

| Digital Storage Oscilloscope | ⬤ | ⬤ | 16M RL | ||

| Differential Probes | ⬤ | > 2 nos. | |||

| Data Timing Generator | ⬤ | ⬤ | DTG5274 with 3 DTGM30 | ||

| Sampling Oscilloscope | ⬤ | ⬤ | ⬤ | TDS8200 with 80E03/80E04 | |

| TPA-R Test Adapter Set | ⬤ | ⬤ | ⬤ | ⬤ | 013-A012-50 |

| TPA-P Test Adapter Set | ⬤ | 013-A013-50 | |||

| 50 Ω terminations (14 nos.) | ⬤ | 015-1022-01 | |||

| SMA Cables (8 nos.) | ⬤ | ⬤ | ⬤ | 174-1428-00 | |

| GPIB USB Controller | ⬤ | ⬤ | ⬤ | ⬤ | National Instruments GPIB-USB-B |

| GPIB Cable | ⬤ | ⬤ | ⬤ | ⬤ |

c. ケーブル・テストのセットアップ

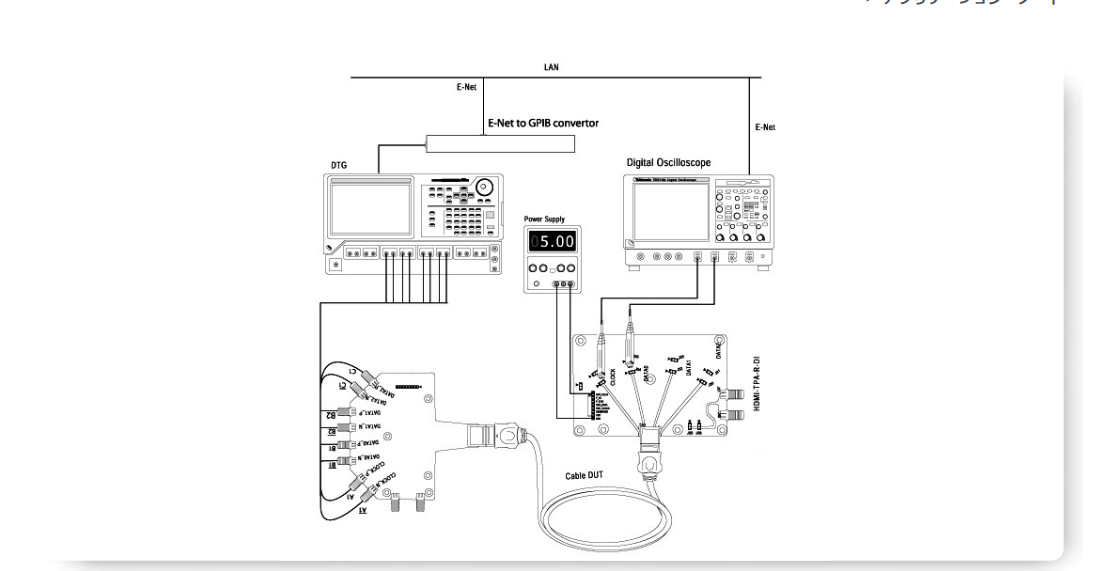

データ・アイ・ダイアグラムのテストについては、図21を参照してください。

イントラペア・スキューのテストについては、図22を参照してください。

インターペア・スキューのテストについては、図23を参照してください。

HDMIコンプライアンス・テスト・ソフトウェアTDSHT3

HDMI物理層の設計や検証を担当するエンジニアには、社内で徹底した検証を実施することが求められています。そのため、数多くのテストを実施する必要があります。

このテストは制限値が厳しいため、正確な測定技術とともに、各種テスト機器の複雑な制御が必要になります。さらに規格では、このテストの多くを、対応しているピクセル分解能ごとに実施するよう要求しているため、複雑さが一層増大します。

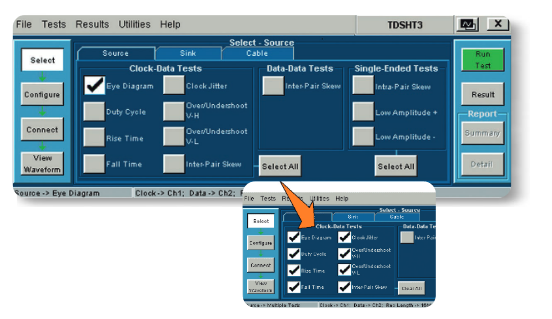

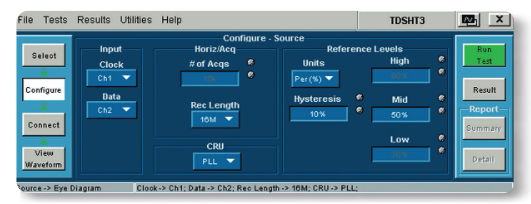

TDSHT3 HDMIコンプライアンス・テスト・ソフトウェアは、ソース、シンク、ケーブルを含むテスト全体を自動化することで、信頼できる結果を提供しつつ、かつてない高効率化を実現します。

信頼性の高い結果

TDSHT3には、ソフトウェア・クロック・リカバリ(SoftCRU) などのHDMI CTSコンプライアンス・テスト手順が組み込まれ ており、また、正確なアイ開口測定やバイオレーション・テスト によって、信頼性の高い結果が得られます。シンク・テストは、 クローズド・ループ測定によってオペレータによらず正確に実施 され、正確なジッタ・コンポーネントによって一貫した測定結果 が得られます。確かな測定技術と自動化によってエラーがなくな ることで、結果の信頼性が上がります。

検証サイクルの短縮

TDSHT3は、高度な自動化によって迅速な検証が可能になりま す。TDSHT3は、DTGやAWGをリモート制御し、複雑なテス ト・プロセスを自動化することで、何時間もかかったシンク機器 のテストを数十分に短縮できます。また、Select Allボタンひと つで多数のソース・テストが実行できるため、効率が上がります。 さらに、CSVフォーマットのサマリや詳細なレポートも、ボタ ンひとつで即座に作成できます。

検証のための包括的なソリューション

TDSHT3では、さまざまなテストによって、規格に対する徹底 的な検証が可能です。ソース、シンクおよびケーブルの機器をす べてテストできます。TDSHT3を使用すれば、オシロスコープ、 任意波形ゼネレータ、データ・タイミング・ゼネレータ、テス ト・フィクスチャ、TDRなどが揃った包括的なソリューション によって、信頼性の高い検証が可能になります。

TDSHT3を用いたテストの実施

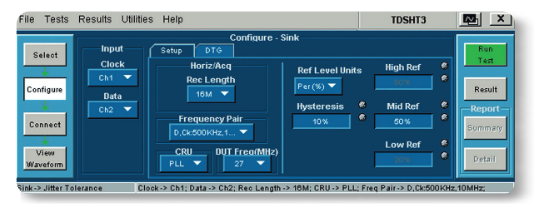

Select Allを選択し、Run Testボタンを押すだけで、さまざまなテストすべてを実行できます。シンク・テストを呼び出す場合は、Sinkタブを選択します。

使いやすいユーザ・インタフェースにより、設定作業で迷うこともありません。

シンク・テストでは、振幅や周波数などジッタ関連のさまざまなパラメータを簡単に設定でき、ソフトウェアがDTGやAWGへのファイル転送を管理することで、テストが自動化されます。

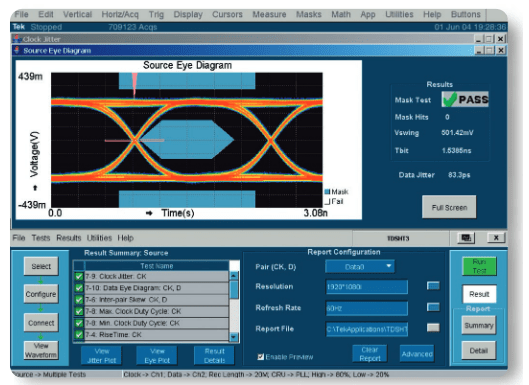

Run Testボタンを押すとテスト・プロセスが開始され、すべてのテストが実施された後、以下のように、該当するグラフや結果のサマリが表示されます。

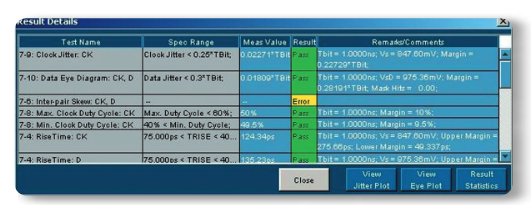

Result Detailsボタンを押すと、制限値や測定値に関する詳しい情報が得られます。

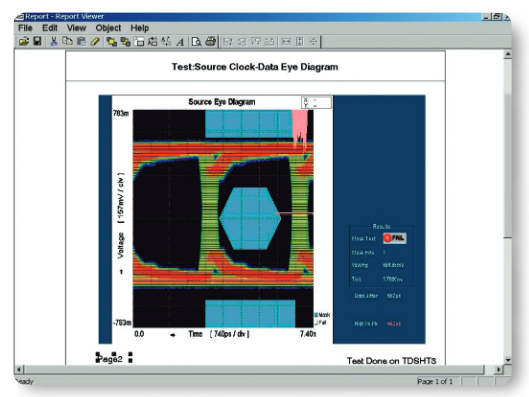

レポートは、ボタンひとつで即座に作成されます。レポートはPDFなどの一般的なフォーマットにも簡単に変換できます。

また、Summaryボタンを押して、CSVフォーマットにすることもできます。これは、複数のポートをテストし、サマリとして文書化する場合に非常に便利です。CSVは、Excelをはじめとする他の一般的なフォーマットへの変換も簡単です。

『TDSHT3 Quick Start User Manual』では、HDMIシンク・テストの実施例を紹介しています。

TDSHT3を使用するメリット

HDMIコンプライアンス・テスト・ソフトウェア TDSHT3に より、数日かかった検証が数十分に短縮できます。確かな測定技 術とクローズド・ループ測定により、信頼性の高い結果が得られ ます。高度な自動化によりテスト時間が短縮でき、人的ミスも最 小限に抑えられます。また、さまざまなテスト機器と組み合わせ ることで、HDMIテスト用の包括的ソリューションが得られます。

まとめ

HDMI(High-Definition Multimedia Interface)技術が急速 な成長を遂げています。その結果、HDMI規格への適合を証明す ることに関心が高まっています。製品開発でHDMI物理層の設計 や検証を担当するエンジニアは、さまざまなテストを迅速かつ確 実に実施し、効率アップを図ることが必要になります。

数々の厳格なテストには今までにない複雑さも加わり、エンジニアはさまざまな課題を抱えています。マージンが厳しいため、慎重な測定が要求され、エラーの要因についても十分に理解していなければなりません。

TDSHT3を使用すれば、さまざまなテストを迅速かつ確実に実施して効率アップを図ることができます。

参考文献

- HDMIスペシフィケーション

- CTS(コンプライアンス・テスト・スペシフィケーション)

- 高速差動データ信号伝送と測定-入門書(テクトロニクス)

- TDS8000B型デジタル・サンプリング・オシロスコープを用いた差動インピーダンス測定-アプリケーション・ノート(テクトロニクス)

- Measuring Controlled Boards with TDR -アプリケーション・ノート(テクトロニクス)

- TDSHT3 Quick Start User Manual -マニュアル(テクトロニクス)