はじめに

DRAM(Dynamic Random Access Memory)は、多様な性能を持ち、コンピュータや組み込みシステムなどのメモリ・システムで広く採用されています。この入門書では、DRAMの概要、DRAM開発の将来性、評価によるメモリ設計の改善について説明します。

DRAMのトレンド

コンピュータで使用されるメモリには、大容量、高速化、低電力化、小型化などの要求が常にあります。これらのニーズにより、DRAM技術の進歩は加速されています。主要なDRAMは、SDRAM(Synchronous DRAM)、DDR(Double Data Rate)SDRAM、DDR2(Double Data Rate 2)SDRAM、DDR3(DoubleData Rate 3)SDRAMなどによって発展してきました。また、DIMM(Dual Inline Memory Module)におけるコンピュータ・メモリの使用によっても発展してきました。DIMMは、アンレジスタードDIMMに始まり、レジスタードDIMM、FB-DIMM(Fully Buffered DIMM)へと発展してきました。

大容量、高速化、低電力化、小型化が進んでいるのはコンピュータ用メモリだけではありません。組み込みシステム・アプリケーションにも同様の要求があり、やはりDRAMを使用しています。

しかし、コンピュータと組み込みシステムでは、メモリ・システム の実装方法が異なります。通常、コンピュータ・メモリは、組み 立て時にインストールが簡単になるように、差し込み式のDIMM を採用しています。ユーザは、コンピュータを購入した後、DIMM を追加、交換することでメモリをアップグレードします。この結 果、コンピュータで使用されるメモリは、現在または将来のコンピュータと高いレベルでの互換性が必要になります。また、DIMM で使用されるメモリとも高いレベルでの互換性が必要になります。 互換性には2種類あります。まず、コンピュータ・メーカが使用 する、数多くのメモリ・コントローラ・ハブと互換性がなければ なりません。次に、コンピュータのメモリ・システム内で異なっ たメーカのメモリと混在した場合でも互換性がなければなりま せん。公開されたメモリの規格は、メモリの互換性に貢献します。

一方、組み込みシステムでは通常固定式のメモリを使用し、ユー ザは購入後、メモリ・システムを変更することはできません。し たがって、組み込みシステム・メーカは、どのメーカのメモリを 組み込みシステムで使用するかを決定します。一つのメモリ製造 メーカの特定のメモリを使用することにより、性能とコストを最 適化することは、一般的に行われることです。結果として、組み 込みシステムでは、コンピュータ・システムと比べると、製造メー カ間における相互運用性はそれほど重要ではありません。

JEDEC(Joint Electron Device Engineering Council)は、 JEDEC規格としてメモリの仕様を策定しています。JEDECは、 メモリ製造メーカ、コンピュータ・メーカ、テスト機器製造メーカ などから構成される非営利団体です。JEDEC規格は一般に公開 され、メモリを実装する製造メーカ間で異なったメーカのメモリ、 コンピュータ・メモリ・コントロール・ハブと相互運用できるよ う、必要な仕様を定義します。この規格では、物理的な特性、 DIMMの基板レイアウト、電気信号、レジスタの定義、機能動作、 メモリ・プロトコルなどを規定します。JEDECの仕様にしたがっ て適合性をテスト、評価することで、他の製造メーカの製品との 間で、メモリ動作が確実に相互運用できることが確認できます。

最新のDRAM設計では、コンピュータや組み込みシステムがメモリ に対して要求する、より大容量、高速化、低電力化、小型化とい う要求を満たしています。この結果、メモリ容量は増え、バンク数 は増え、バースト長は長くなり、供給電圧は低下し、ロジック電 圧スイングは小さくなり、クロック・レートとデータ・レートは 高速になり、メモリ・チャンネルの実装は多チャンネルのパラレ ル信号から高速のシリアル信号になり、回路の実装密度は上がる などの難問に直面しています。設計エンジニアは、このような課 題に対して、新しい設計技術、設計ツール、評価、デバッグ方法 で対応しています。

メモリのクロック・レートが高速になり、ロジック電圧スイング が低下すると、確実なメモリ動作にとってはシグナル・インテグ リティが重要な問題となります。このため、メモリ・システムの シグナル・インテグリティの改善が、新しいDRAMの機能として 注目されるようになりました。新しい機能としては、ダイナミッ ク・コントロールODT(オン・ダイ・ターミネーション)、OCD (オフチップ・ドライバ)校正、AMB(拡張メモリ・バッファ) によるFB-DIMMなどがあります。

DRAM

他のメモリと比べたDRAMの利点は、IC(集積回路)上のメモ リ・セルあたりの回路を少なくできるという点です。DRAMのメ モリ・セルは、キャパシタに電荷を蓄えることを基本としています。 一般的なDRAMのセルは、1つのキャパシタと1つまたは3つの FET(電界効果トランジスタ)で構成されています。一般的な SRAM(Static Random Access Memory)のメモリ・セルは 6つのFETを使用していますので、同じサイズのICではメモリ・ セルの数が少なくなります。SRAMは使い方が簡単で、インタ フェースも容易であり、DRAMに比べるとデータのアクセス時間 が高速です。

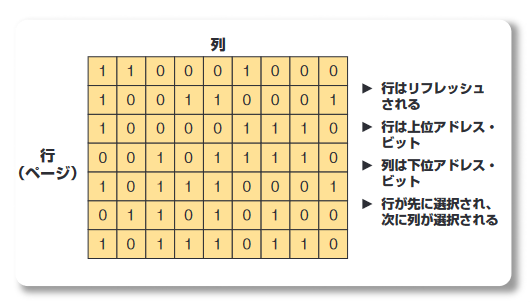

DRAMのコア・アーキテクチャは、行と列による二次元の配列によるメモリ・セルで構成されています(図1参照)。メモリ・セルへのアクセスには、2つの手順が必要です。まず行を指定し、次に選択された行の列を指定します。言い換えると、まずDRAM ICの一つの行すべてが内部的に読み出され、次に、列アドレスによってDRAM IC I/O(入力/出力)ピンに読み書きされる行の列を選択します。

DRAMの読み出しでは、メモリ・セルの行データは読み出しによって失われます。したがって、行で読み書きが完了した後、行データを同じ行に書き戻す必要があります。この動作はプリチャージと呼ばれ、行における最後の動作になります。これは、新しい行にアクセスする前に完了する必要があり、開いた行を閉じることになります。

コンピュータ・メモリ・アクセスの解析によると、メモリ・アドレスのシーケンシャルな読み出しが、メモリ・アクセスの最も一般的なタイプです。データの読み書きに比べ、コンピュータ・インストラクションの読み出しがより一般的であることから、これは妥当であると言えます。また、メモリにおけるほとんどの読み出しのインストラクションは、ブランチやサブルーチンへのジャンプが発生するまではシーケンシャルです。

DRAMの行はメモリ・ページとも呼ばれ、行が開くと、その行の 複数のシーケンシャルまたは異なった列アドレスにアクセスでき ます。同じメモリ・ページのメモリ・セルにアクセスする際、行 アドレスを再送する必要がありませんので、メモリのアクセス・ スピードが上がり、メモリのレイテンシが低減します。結果とし て、行アドレスは上位のアドレス・ビットであり、列アドレスは 下位のアドレス・ビットとなります。行と列のアドレスは異なっ た時間に送られますので、パッケージのピン数、コスト、サイズ を小さくするため、行アドレスと列アドレスは同じDRAMピンで 多重化されます。電力消費は列の数に関係しますので、一般的に、 行アドレスのサイズは列アドレスに比べて大きくなります。

初期のDRAMには、RAS#(行アドレス・セレクト、アクティブ・ロー)やCAS#(列アドレス・セレクト、アクティブ・ロー)などのコントロール信号があり、実行する行や列のアドレスを選択します。その他のDRAMのコントロール信号には、読み書きの選択のためのWE#(ライト・イネーブル、アクティブ・ロー)、DRAMを選択するためのCS#(チップ・セレクト、アクティブ・ロー)、OE#(出力イネーブル、アクティブ・ロー)があります。初期のDRAMのコントロール信号は非同期であり、シーケンスやDRAMの動作モードを決めるための時間関係をカバーするため、いくつかのタイミング仕様があります。

初期のDRAMの読み出しサイクルには4ステップあります。まず、 アドレス・バスの行アドレスでRAS#がローになります。二番目 に、アドレス・バスの列アドレスでCAS#がローになります。三 番目に、OE#がローになってDQデータ・ピンにリード・データ が現れます。最初のステップから三番目のステップまでの、デー タがDQピンに現れるまでの時間をレイテンシと呼びます。最後 のステップは、RAS#、CAS#、OE#がハイ(イナクティブ)に なり、データ消滅後の行データの復元のための、内部のプリチャージ 完了を待ちます。最初のステップから最後のステップが完了する までの時間を、メモリ・サイクル時間と呼びます。これらの信号 のタイミングはエッジのシーケンスに関係し、非同期です。初期 のDRAMには、同期クロックの動作はありませんでした。

DRAMのメモリ・セルは、データ消失を避けるためにリフレッシュ する必要があります。このリフレッシュは、キャパシタの電荷が 失われる前に実行される必要があります。メモリのリフレッシュ はメモリ・コントローラによってコントロールされ、リフレッシュ 時間の仕様はDRAMメモリによって異なります。メモリ・コント ローラは、RAS#のみのサイクルと行アドレスでリフレッシュを 実行します。RAS#のみのサイクルの最後が、RAS#のみのサイ クルのアドレスの行データを復元するためのプリチャージ動作に なります。通常、メモリ・コントローラは、RAS#のみのリフレッ シュ・サイクルに必要なすべての行アドレスをシーケンシャルに 作成するための行カウンタを持っています。

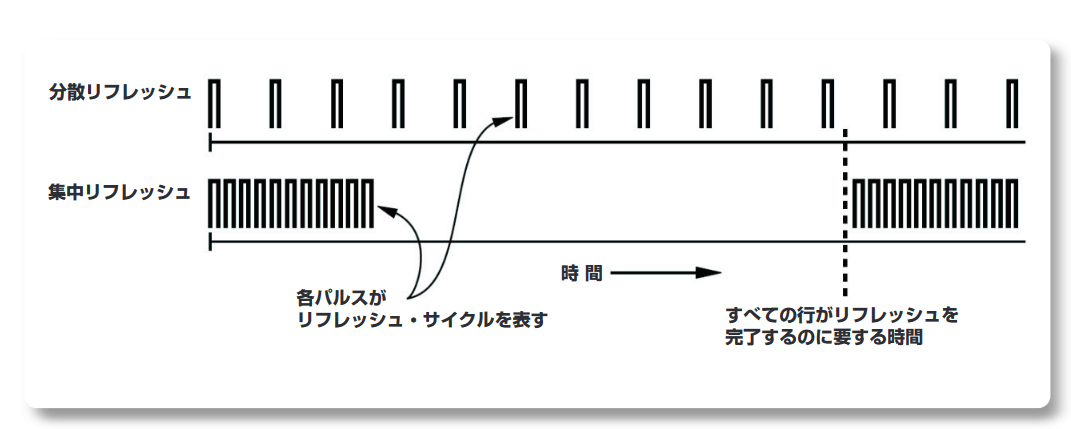

リフレッシュには、2通りの方法があります(図2参照)。一つは、 メモリ・コントローラがバースト・リフレッシュ・サイクルによっ てすべての行を連続的にリフレッシュし、その後、プロセッサに メモリ・コントロールを戻すという方法です。最長リフレッシュ時 間になる前に、次のバースト・リフレッシュを実行します。もう 一つの方法は、メモリ・コントローラが、リフレッシュ・サイクル と通常のプロセッサ・メモリ動作をインターリーブする方法です。 この方法では、リフレッシュ・サイクルを最長リフレッシュ時間 まで広げることができます。

初期のDRAMでは、DRAM IC内にリフレッシュ・カウンタを設け、 連続的に行アドレスを生成しました。DRAMの内部では、リフ レッシュ・カウンタは、メモリ・アレイの行アドレスをコントロー ルするマルチプレクサの入力です。外部アドレス入力ピンの行 アドレスからも、マルチプレクサに入力されます。この内部リフ レッシュ・カウンタ回路により、メモリ・コントローラのリフレッ シュ・カウンタ回路が不要になります。このようなDRAMでは、 RAS#の前のCAS#サイクルにより、内部で生成する行アドレス を使ってリフレッシュ・サイクルを実行します。

SDRAM

DRAMの非同期動作では、同期プロセッサとインタフェースをと る際、多くの問題が発生します。SDRAM(Synchronous DRAM) は、DRAMの動作を他のコンピュータ・システムと同期させるこ とにより、CE#(チップ・イネーブル、アクティブ・ロー)、 RAS#、CAS#、WE#などのエッジ・トランジションに基づいた、 すべての異なったメモリ動作モードを定義する必要がなくなりま す。SDRAMでは、クロック信号とメモリ・コマンドの概念を追 加しました。メモリ・コマンドのタイプは、SDRAMクロックの 立上りエッジにおけるCE#、RAS#、CAS#、WE#信号のステー トで決まります。データ・シートには、CE#、RAS#、CAS#、 WE#信号のステートによるメモリ・コマンドが表形式で記載され ています。

例えば、Activeコマンドは、メモリの行(ページ)を開けるよう SDRAMに行アドレスを送ります。次に、Deselectのコマンド・ シーケンスにより、列アドレスと共にリード/ライト・コマンド を送る前のタイミング要求を満足させます。Activeコマンドでメ モリの行(ページ)が開くと、その行(ページ)のデータについ てリード/ライト・コマンドが動作できます。別な行を開く前に、 Prechargeコマンドで行を閉じる必要があります。

DDR SDRAM

DDR(Double Data Rate)SDRAMでは、クロック・レート の高速化、データのバースト転送、1クロック・サイクルあたり 2ビットのデータ転送により、メモリ・データ・レート性能を向上 しています(表1参照)。DDR SDRAMでは、一つのリード/ライ ト・コマンドで複数のメモリ・ロケーションがバースト・アクセ スされます。メモリのリード動作では、Activateコマンドに続い てReadコマンドを送ります。メモリは、レイテンシの後、クロッ ク・サイクルあたり2つのメモリ・ロケーションのデータ・レー トにおいて連続した2、4、8メモリ・ロケーションで応答します。 したがって、2つの連続したクロック・サイクルで4つのメモリ・ ロケーションが読み書きされます。

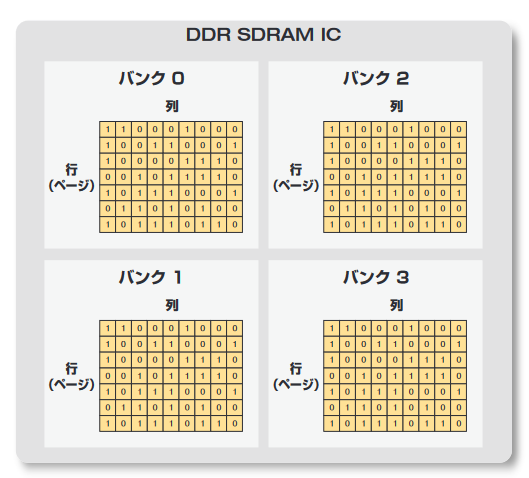

DDR SDRAMには複数のメモリ・バンクがあり、複数のインターリーブによってメモリ・アクセスでき、メモリ帯域が拡がります。バンクとはメモリの配列であり、2つのバンクは2列のメモリを、4つのバンクは4列のメモリを表します(図3参照)。4バンクでは、バンク・アドレスのために2ビットが必要になります(BA0&BA1)。

例えば、4バンクのDDR SDRAMでは、次のように動作します。まず、Activeコマンドで第一バンクの行が開きます。二番目のActiveコマンドで第二バンクの行が開きます。これで、第一バンクでも第二バンクでも、任意のRead、Writeの組み合わせでコマンドを送ることができます。バンクでの読み書き動作が完了すると、Prechargeコマンドによって行が閉じ、新しい行を開くActiveコマンドの準備を終えます。

DDR SDRAMに必要な電源は、開く行とバンク数に関係します。開く行の数が多いほど電力が大きくなり、行サイズが大きいほど電力が大きくなります。したがって、低電力のアプリケーションでは、各バンクでは一つだけ行を開くようにし、複数のバンクで同時に行を開かないようにします。

| DDR SDRAM | データ・レート | メモリ・クロック |

| DDR-266 | 266Mbps/ピン | 133MHz |

| DDR-333 | 333Mbps/ピン | 166MHz |

| DDR-400 | 400Mbps/ピン | 200MHz |

表1:DDR SDRAMのデータ・レートとクロック・スピード

連続したメモリ・バンクで連続したメモリ・ワードをインターリーブすることは、バンク・アドレス・ビットが下位のアドレス・ビットに接続されている場合にサポートされます。バンク・アドレスが上位のアドレス・ビットに接続されている場合に、連続したメモリ・ワードは同じメモリ・バンクに存在します。

DDR2 SDRAM

DDR2 SDRAMは、DDR SDRAMに対していくつかの改良が 施されています。DDR2 SDRAMのクロック・レートはより高 速になっており、メモリのデータ・レートも高速になっています (表2参照)。クロック・レートが高速になっていますので、確実 なメモリ動作のためにはシグナル・インテグリティが重要になり ます。クロック・レートが高速になると、回路基板の信号経路は 伝送ラインになり、信号経路の終端における正しいレイアウトと ターミネーションが重要になります。

アドレス、クロック、コマンド信号は単一方向であり、回路基板 で終端されていますので、終端処理は比較的簡単です。データ信 号とデータ・ストローブ信号は双方向です。メモリ・コントロー ル・ハブは書き込み動作においてこれらの信号をドライブします。 DDR2 SDRAMは読み込み動作のときにこれらの信号をドライブ します。複数のDDR2 SDRAMが同一のデータ信号とデータ・ ストローブ信号に接続されることが、複雑さを増しています。こ の複数のDDR2 SDRAMはメモリ・システム上の同一のDIMM 上にある場合と、別のDIMM上にある場合があります。結果と して、データ信号とデータ・ストローブ信号のドライバ/レシー バは、リード/ライト動作、また、どのDDR2 SDRAMがアク セスされるかによって常に変化します。

DDR2 SDRAMでは、ODT(オンダイ・ターミネーション)に よりデータ信号とデータ・ストローブ信号のシグナル・インテグ リティを改善しています。ODT信号では、オン・ダイ・ターミ ネーションが可能であり、またDDR2 SDRAMの拡張モード・ レジスタでオン・ダイ・ターミネーションの値(75Ω、150Ω 等)をプログラムできます。オン・ダイ・ターミネーションの値 と動作は、メモリ・コントローラ・ハブによりコントロールされ、 DDR2 SDRAM DIMMの場所とメモリ動作(リードまたはライト) により決定されます。ODTにより、電圧マージン、スルー・レート が増え、オーバシュートやISI(Inter-Symbol Interference)が 減り、有効なデータ・ウィンドウのアイ・ダイアグラムが大きく なることで優れたシグナル・インテグリティが実現されます。

DDR2 SDRAMのメモリ・システム電源は1.8V動作に減少しており、これはDDR SDRAMの2.5Vに比べて72%になります。実装によっては、行内の列が減ることで、リードまたはライトの低電力化が実現できます。

| DDR2 SDRAM | データ・レート | メモリ・クロック |

| DDR2-400 | 400Mbps/ピン | 200MHz |

| DDR2-533 | 533Mbps/ピン | 266MHz |

| DDR2-667 | 667Mbps/ピン | 333MHz |

| DDR2-800 | 800Mbps/ピン | 400MHz |

表2:DDR2 SDRAMのデータ・レートとクロック・スピード

動作電圧が低いことの利点は、ロジック電圧スイングを小さくで きることにもあります。同じスルー・レートでは、電圧スイングが 小さいとロジックのトランジション速度が増し、高速のクロック・ レートをサポートすることができます。さらに、データ・スト ローブ信号を差動信号にプログラムすることもできます。データ・ ストローブ信号を差動信号にすることで、ノイズ、クロストーク、 ダイナミック消費電力、EMI(電磁妨害)を低減して、ノイズ・ マージンを高めることができます。データ・ストローブ信号は、 DDR2 SDRAMの拡張モード・レジスタで、差動又はシングル エンド信号に設定されます。

DDR2 SDRAMでは、新機能として追加的なレイテンシが導入されています。これは、メモリ・コントローラ・ハブに柔軟性を持たせることにより、Read/Write信号をActivateコマンドの直後に送れるようにしています。これはメモリのスループットを最適化し、DDR2 SDRAMの拡張モード・レジスタによって追加のレイテンシをプログラミングすることで設定されます。

DDR2 SDRAMでは、8バンクを使用することで1Gビット及び2Gビットのデータ帯域を実現しています。8ビット・バンクは、異なったメモリ・バンク動作のインターリーブにより、大きなDDR2 SDRAMメモリのアクセスに柔軟性を持たせることができます。また、大きなメモリにおいて、DDR2 SDRAMは8までのバースト長をサポートします。

DDR2 SDRAMのデータ・シートは100ページ以上にもなり、ここで説明した機能は主要な機能の一部にしか過ぎません。機能と詳細については、DDR2 SDRAMのデータ・シートをご参照ください。

DDR3 SDRAM

DDR3 SDRAMは、DDR2 SDRAMの性能をさらに改善しています。DDR3 SDRAMは、さらなる高速のデータ・レートとクロック・スピードを実現しています(表3参照)。さらに、DDR3SDRAMでは動作電圧が1.5Vになり、DDR2 SDRAMの1.8Vに比べて83%になっています。DDR3 SDRAMは、FB-DIMM2(Fully Buffered DIMM2)の実装に使用されるメモリです。DDR3 SDRAMの仕様は策定中であり、JEDECによって承認されるまでは変更されることがあります。

DDR3 SDRAMの仕様については、JEDECのウェブ・サイト(www.jedec.org)で小委員会に参加でき、承認された仕様についても参照することができます。

DIMM

DIMM(Dual Inline Memory Module)は、コンピュータで使用するプラグイン・タイプのメモリ・モジュールです。DIMMには、いろいろな物理的なサイズ、メモリ・データ幅、ランク、メモリ・サイズ、メモリ・スピード、メモリ・アーキテクチャがあります。JEDECはDIMMの規格を制定し、新しいメモリ・タイプ、メモリ・アーキテクチャによる、新しいDIMM規格を引き続き策定しています。

DIMMの物理サイズ

標準サイズのDIMMは、デスクトップ、ワークステーション、 サーバで使用されます。SO-DIMM(Small Outline DIMM) は小型のDIMMで、ラップトップなどのスペースが限られた用途 で実装されます。2枚のSO-DIMMをコンピュータのマザーボード に平行に、エッジ・コネクタを隣どうしに配置したものをバタフ ライ・コンフィグレーションと呼びます。2つのエッジ・コネク タを蝶々の体に、SO-DIMMを開いた羽と見ることができます。 Mini-DIMM(ミニチュアDIMM)はSO-DIMMより小型で、シン グル・ボード・コンピュータで使用されます。VLP-DIMM(Very Low Profile DIMM)は高さが低く、ブレード・サーバで使用され ます。

| DDR3 SDRAM | データ・レート | メモリ・クロック |

| DDR3-800 | 800Mbps/ピン | 400MHz |

| DDR3-1066 | 1066Mbps/ピン | 533MHz |

| DDR3-1333 | 1333Mbps/ピン | 667MHz |

| DDR3-1600 | 1600Mbps/ピン | 800MHz |

表3:予測されるDDR3 SDRAMのデータ・レートとクロック・スピード

| DIMM | 4 I/Os per IC | 8 I/Os per IC | 16 I/Os per IC |

| 1ランク | 16 ICs | 8 ICs | 4 ICs |

| 2ランク | 32 ICs | 16 ICs | 8 ICs |

| 4ランク | 64 ICs | 32 ICs | 16 ICs |

表4:DIMMのランクとメモリICのデータI/O数による、DIMMあたりのメモリIC数(ECCなし)

DIMMのデータ幅

DIMMデータ幅は、ECC(エラー検出コード)のサポートに依存します。ECCは8ビットのチェック・ビットで、エラーの検出、修復に使用されます。標準のDIMMデータ幅は、ECCなしで64ビット、8ECCビット付きで72ビットです。

DIMMのランク

ランクとは、DIMMにおいて64ビット・データまたはECC付き で72ビット・データをサポートする、メモリ・デバイス・グルー プ数をさします。ランク2では、1枚のDIMM上に2つのメモリ・ デバイス・グループが存在します。ランク4では、1枚のDIMM上 に4つのメモリ・デバイス・グループが存在します。表4では、 ECCなしの64ビット・データ幅をサポートする、DIMM1枚の メモリICの数を示します。DIMMの両サイドにすべてのメモリIC を載せるだけのスペースがないことがあります。このような場合は、 メモリICを積み重ねて実装します。

DIMMのメモリ・サイズと速度

DIMMのメモリ・サイズは、使用されるメモリICのサイズとDIMM構成に依存します。512Mb(メガ・ビット)のメモリICは、異なった構成で設計されることがあります(表5参照)。DIMMの速度は、DIMMで使用されるDDR、DDR2、DDR3 SDRAMのクロック・スピードに依存します。

DIMMのアーキテクチャ

DIMMには、主にUDIMM、RDIMMそしてFB-DIMMという3種類のアーキテクチャがあります。どのDIMMアーキテクチャにも長所、短所があります。

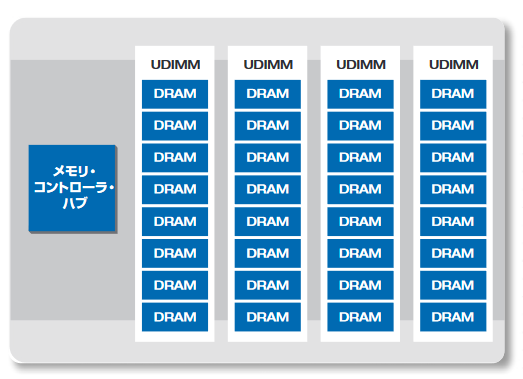

UDIMMはアンレジスタードDIMMです。UDIMM(Unregistered DIMM)では、DIMM上でDDR、DDR2、DDR3 SDRAM信号を バッファリングしていません(図4参照)。UDIMMは、最初に実 装されたDIMMアーキテクチャです。1枚または2枚のDIMMメ モリ・システムでは、UDIMMが最も高速で低価格です。メモリ・ コントローラ・ハブが、すべてのDRAM信号を直接コントロール します。UDIMM上のメモリ・コントローラ・ハブとSDRAM間に おいては、バッファやレジスタによる遅延はありません。メモリ・ コントローラ・ハブのメモリ・チャンネルにおけるUDIMMの数 は、シグナル・インテグリティによって制限されます。シグナル・ インテグリティは、メモリ・クロックの高速化、トレース長の増 加、メモリ・チャンネルあたりのUDIMM数の増加、UDIMMの ランク数の増加によって劣化します。メモリ・コントローラ・ハ ブは、すべてのコネクタ、トレース、トレース・ブランチ、 SDRAMピンをモニタします。ツリー・スタブ構造でのインピー ダンスによる問題は、クロック周波数と、メモリ・チャンネルが 確実に動作できるUDIMM数に影響します。

| ページ・サイズ | I/Oピン数 | バンク数 |

| 32メガ・ビット | 4 | 4 |

| 16メガ・ビット | 8 | 4 |

| 8メガ・ビット | 16 | 4 |

表5:512Mb(メガ・ビット)メモリICの構成例

メモリ・システムのUDIMM数を増やすには、独立した別のメモリ・チャンネルを持ったメモリ・コントローラ・ハブを使用する方法があります。2つの独立したメモリ・チャンネルにより、メモリ・チャンネルあたり1枚のUDIMMで、合計2つの高速UDIMMがサポートできます。

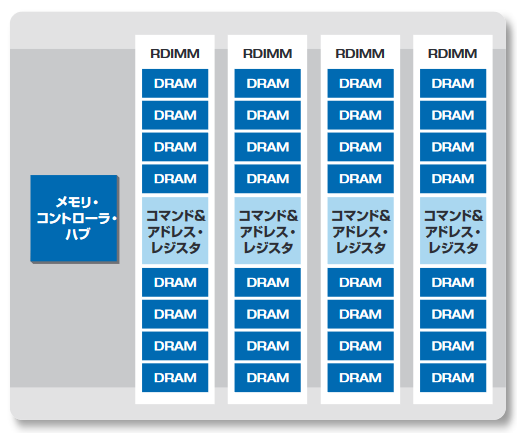

RDIMMはレジスタードDIMM(Registered DIMM)です。 RDIMMではSDRAMクロック、コマンド信号、アドレス信号を バッファリングすることで、ツリー・スタブ構造による問題を軽 減します(図5参照)。クロック信号はPLL(Phase Lock Loop)でバッファされ、コマンド信号とアドレス信号はレジス タ・ラッチでバッファされます。通常RDIMMは、1個のPLL IC と2個のレジスタICと共に実装されます。メモリ・コントローラ・ ハブ・クロック、コマンド信号、アドレス信号は、マザーボード 配線、DIMMコネクタ、RDIMMレジスタ、RDIMM PLLのイン ピーダンスを見ます。このツリー・スタブ構造により、メモリ・ チャンネルでより多くのRDIMMが使用でき、高速になります。双 方向のDQデータ・ラインやDQSデータ・ストローブ・ラインは、 バッファリングされてないため、信号負荷の低減による利点はあ りません。また、RDIMMでは、コマンドとアドレス信号をラッ チしてレジスタへ渡すために1クロック・サイクルが必要になり ますので、メモリ・アクセス時間は、UDIMMに比べて1クロッ ク分遅くなります。

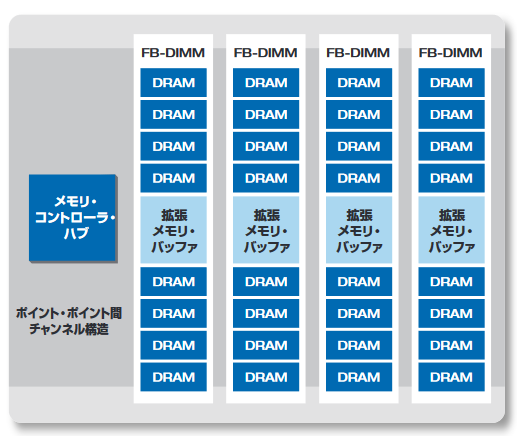

FB-DIMMは、フル・バッファ型のDIMMです。FB-DIMMではDDR2 SDRAMを使用し、FB-DIMM2ではDDR3 SDRAMを使用します。すべてのDDR2 SDRAMとDDR3 SDRAM信号は、FB-DIMMとFB-DIMM2上のAMB(拡張メモリ・バッファ)ICのメモリ・システムによりバッファされます(図6参照)。FBDIMMとFB-DIMM2では、異なったAMBが使用されます。

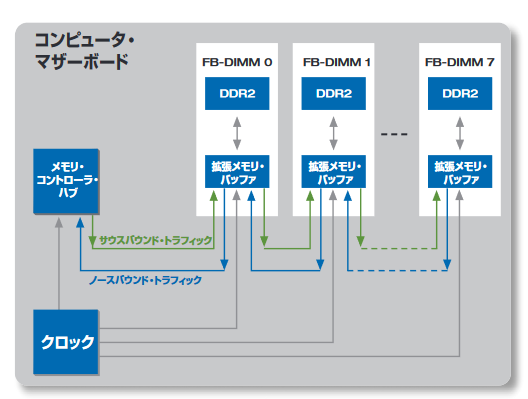

メモリ・コントローラ・ハブの隣にある最初のFB-DIMMは、最 高24本の高速差動信号でメモリ・コントローラ・ハブと通信し、 最高24本の高速差動信号で隣接したFB-DIMMと通信します(図 7参照)。これらの信号は単一方向、ポイント・ポイント間、高速 シリアル技術によりコマンドとデータを送ります。10本の信号に より、メモリ・コントローラ・ハブからAMBに向かってサウスバ ウンド・トラフィックを送り、12~14本の信号により、AMBか らメモリ・コントローラ・ハブに向かってノースバウンド・トラ フィックを送ります。FB-DIMMのアーキテクチャは、最新の高 速デジタル設計トレンドにしたがい、ツリー・スタブ構造による パラレル・バスから、少ないポイント・ポイント間、高速シリア ル・レーンになっています。

FB-DIMMアーキテクチャは、FB-DIMM上のDDR2メモリから、 AMBを経由して、シリアル・ノースバウンドのポイント・ポイン ト間信号をメモリ・コントローラ・ハブへ、メモリのフルスピー ドでデータ転送するように設計されています。シリアル・フレー ムは12ビット長で、その幅は10サウスバウンド信号レーンから 14ノースバウンド信号レーンです。12シリアル・ビットは、一 つのDDR2クロック・サイクルで転送されます。したがって、 DDR2のクロック周波数を12倍することで、高速シリアル・レーン のデータ・レートが求められます。同様に、DDR2のデータ・レー トを6倍することで、高速シリアル・レーンのデータ・レートが 求められます(表6参照)。コンピュータのマザーボードのメモ リ・システム・クロックは、DDR2クロックの半分です。AMB のPLL機能により、DDR2 SDRAMクロックが2倍になります。

サウスバウンド・レーンは10に固定されており、ノースバウンド・レーンは12~14です。レーンに12シリアル・ビットをかけると、フレームのビット数が求められます(表7参照)。サウスバウンド・レーンは10に固定されていますので、1フレームあたり120ビットです。ノースバウンド・レーンは、FB-DIMMでECCが使用されているか、また使用されるシリアルCRCビッ

| DDR2 SDRAM | データ・レート | DDR2クロック | シリアル・データ・レート |

| DDR2-533 | 533Mbps/ピン | 266MHz | 3.2Gbps |

| DDR2-667 | 667Mbps/ピン | 333MHz | 4.0Gbps |

| DDR2-800 | 800Mbps/ピン | 400MHz | 4.8Gbps |

表6:FB-DIMMポイント・ポイント間シリアル・レーンのシリアル・データ・レートは、FB-DIMMのDDR2 SDRAMのスピードに依存します。

| レーン | シリアル・フレームのビット数 |

| 10サウスバウンド レーン | 120 |

| 12ノースバウンド レーン | 144 |

| 13ノースバウンド レーン | 156 |

| 14ノースバウンド レーン | 168 |

表7:FB-DIMMシリアル・データ・ノースバウンド・フレームのサイズは、使用されるノースバウンド・レーン数に依存します。

ト数によって異なります。

例えば、ECCがない場合、ノースバウンド・フレームでは、2つ の64ビット・ワード(2×64=トータル128ビット)が転送さ れる必要があります。1フレームあたり144トータル・ビットの 12ノースバウンド・レーンは、このデータ・レートを取り扱うこ とができます。一方、ECC付きの2つの72ビット・ワード(2× 72=トータル144ビット)をノースバウンド・フレームで転送 する必要があります。1フレームあたりトータル144ビットを転 送する場合、12ノースバウンド・レーンでは144データ・ビッ トにシリアルCRCビットが加わるため不十分ですので、13また は14ノースバウンド・レーンが必要になります。

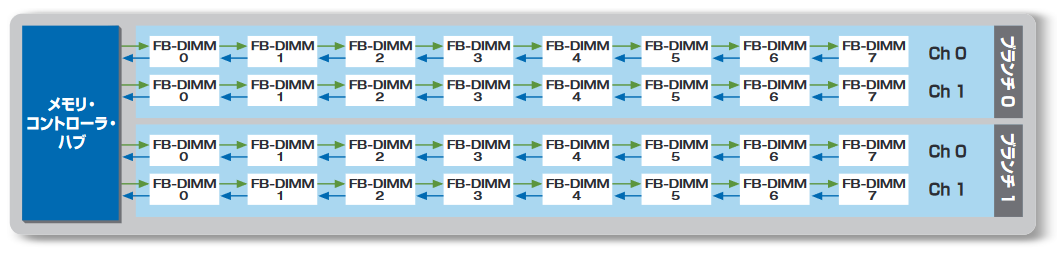

一つのFB-DIMMチャンネルは、最高8つのFB-DIMMをサポート します。メモリ・コントローラ・ハブからは、チャンネルあたり わずか24本の高速信号配線が必要であり、またこれらの配線は 等長である必要はありませんので、FB-DIMMのマザーボードの レイアウトは容易です。一方、UDIMMまたはRDIMMでは、メ モリ・コントローラ・ハブからコマンド、アドレス、データなど、 多くのパラレル信号が必要であり、また正しい動作のためには等 長配線が必要になります。メモリ・チャンネルあたりの少ないFBDIMM信号と簡単な回路基板配線により、メモリ・コントローラ・ ハブはより多くのFB-DIMMメモリ・チャンネルをサポートでき ます(図8参照)。これは、同時に各メモリ・チャンネルをアクテ ィブにできますので、メモリの帯域が拡がることを意味します。

FB-DIMMは、大容量のメモリ・システムが要求されるサーバで使用されています。ハイエンド・ワークステーションも、FBDIMMを使用すると予想されています。

SPD (Serial Presence Detect)

SPDは、すべてのコンピュータのDIMMにある機能で、メモリ・ サイズ、スピード、レイテンシ、タイミング、製造メーカなどの DIMMメモリの設定を、コンピュータのパワーオン時にコンピュー タのBIOS(Basic Input Output Software)に知らせます (表8参照)。パワーオン時、BIOSはSPDにより各DIMMの設定 情報をSPDを使って読み取ります。この情報は、メモリ・コント ローラ・ハブの設定や、各UDIMM、RDIMMのDRAMモードと 拡張モード・レジスタの設定に使用されます。SPDは、JEDEC 規格により仕様が定められています。

UDIMMやRDIMMでは、SPDは低速度のI2Cインタフェースを持 った小型の不揮発性メモリICとして、各DIMMに実装されていま す。マザーボードには、ユニークなアドレス(0~7)を持った、 各DIMMスロットのためのI2Cインタフェースがあります。パワー オン時、I2Cインタフェースによって各DIMMスロットがチェック されます。DIMMが実装されている場合、BIOSによってSPDの 値が読み取られます。

FB-DIMMでは、SPDはI2Cインタフェースを持ったAMBによって実装されます。FB-DIMMのI2Cインタフェースは、SM(システム・マネージメント)バスと呼ばれます。SMバスは、各FBDIMMでAMBを設定するために使用されます。

| バイト番号 | 機能の概要 | SPDの16進値 |

| 0 | モジュール製造メーカによってシリアル・メモリに書かれたバイト数を定義 | 80 |

| 1 | SPDメモリ・バイトの総数 | 08 |

| 2 | 基本的なメモリ・タイプ(FPMまたはEDO) | 01 or 02 |

| 3 | メモリ・デバイスの行アドレス数 | 0C |

| 4 | メモリ・デバイスの列アドレス数 | 0A |

| 5 | メモリ・モジュールの物理バンク数 | 01 |

| 6 | モジュールのデータ幅 | 40 |

| 7 | データ幅(続き) | 00 |

| 8 | モジュール電圧インタフェース・レベル | 01 |

| 9 | このモジュールのRASアクセス時間 | 3C |

| 10 | このモジュールのCASアクセス時間 | 0F |

| 11 | モジュール・エラー・コレクション設定のタイプ(ノンパリティ、パリティ、ECC) | 00 or 01 or 02 |

| 12 | リフレッシュ・レート/タイプ | 00 or 83 |

| 13 | プライマリDRAM幅 | 10 |

| 14 | エラー・チェックDRAMデータ幅 | 00 |

| 15~61 | 予備 | 00 |

| 62 | SPDのリビジョン | 00 |

| 63 | バイト0~62のチェックサム | Calculated |

| 64 | 製造メーカのJEDEC IDコード | 2C |

| 65~71 | 製造メーカのJEDEC IDコード(続き) | 00 |

| 72 | 製造メーカの所在地 | 01-08 |

| 73~90 | 製造メーカの部品番号 | Variable |

| 91 | PCBのIDコード | 01-09 |

| 92 | PCBのIDコード(続き) | 00 |

| 93 | 製造の年 | Valiable |

| 94 | 製造の週 | Valiable |

| 95~98 | モジュールのシリアル番号 | Valiable |

| 99~125 | 製造メーカによる特有のデータ | Valiable |

| 126~127 | 予備 | 00 |

| 128~255 | ユーザによるフリー・フォーム(未定義) | FF |

表8:コンピュータのBIOSは、SPDインタフェースによりDIMMの設定を読み取ります。SPDデータはJEDEC規格により仕様が定められています。

メモリ・システムの設計

製品設計の最初の手順は、製品の仕様、製品のアーキテクチャ設計、サブシステム設計です。サブシステム設計の一つがメモリ・システムです。メモリ・システムの設計は、メモリ・サイズ、スピード、電力、現在の規格、新しく策定された規格、既存設計の再利用、その他の要求をもとにして行います。

コンピュータ・チップセット・メーカは、コンピュータのメモリ・システム設計に強く影響を与えます。独自のテスト手順、評価プロセス、製品テストの実験室をもっているコンピュータ・チップセット・メーカもあります。通常、コンピュータ・チップセット・メーカは、自社の互換性テストに合格したメモリ製品をウェブ・サイトで公開しています。

設計シミュレーション

メモリ・システム設計の主要パートは設計シミュレーションです。総合的なメモリ・システム設計のシミュレーションの重要性は軽視できません。たった数Ωの抵抗の変更が、メモリ・システムの確実な動作に大きな影響を与えることは、経験則により知られています。

メモリ・システム設計のシミュレーションでは、プロトタイプの メモリ・システムに計測器を接続することによって生ずるプロー ブ負荷の影響も含める必要があります。プローブ負荷によってプ ロトタイプの動作が止まってしまうような場合は、評価やデバッグが非常にむずかしくなります。また、計測器のプローブ負荷が 加わったプローブ・テスト・ポイントにおける解析も、シミュレー ションする必要があります。データの有効ウィンドウは、メモリ・ コントローラ・ハブ・ドライバからSDRAMのピンまでの信号配 線にともなって変化します。

プロービングするテスト・ポイントは、レシーバ・ピンにできるだけ近くとり、レシーバでの信号が観測できるようにします。これが不可能な場合や、インターポーザやテスト・アダプタ基板、特殊なプロービング・フィクスチャを使って信号にアクセスします。このプロービング・フィクスチャなども、SDRAM信号や信号測定の影響を理解するため、設計シミュレーションに含めます。

設計評価

設計において新しいDRAMの機能を使う場合、新しい設計シミュレーションの技術から、新しいBIOS動作まで、新しい設計手法と技術が必要になります。その結果、DRAM設計の実装では、確実なメモリ動作のための回路基板の製作からソフトウェア動作まで、完全な評価とテストが必要になります。設計の実装評価が十分に行われないために発生するメモリの間欠的なエラーは、製品の信頼性を損なうことになります。さらに顧客は、JEDECや他のメーカによって定義された、各種のコンプライアンス・テストを満足するような製品を要求することがあります。

評価手法

どのような設計の実装でも、効率的ですばやく設計問題をデバッグするための手法は大事なことです。短時間かつタイムリーに製品投入しなければならない場合、設計時の早い段階で評価/デバッグの計画が必要になります。計画には、以下のような項目を盛り込みます。

-新しい設計要素は何か、再利用する設計要素は何か。

過去の設計から、避けるべきことは何か、変更すべきことは何か。

どの程度の評価、テストが必要か。テストでは特殊な動作モード、信号パターンが必要か。

-特殊なデザイン・イン機能は必要か(プロービング・テスト・ポイントまたはテスト・フィクスチャ)、プロトタイプのプロービングのためのシミュレーション解析が必要か、ハードウェアを実行するための特殊なソフトウェアが必要か。

-環境試験が必要か(温度、湿度等)。

-デバッグするための回路動作の視覚的な検証方法はあるか。

-規定されたコンプライアンス・テストは必要か。評価/デバッグ・テスト・ポイントを使って製造時に製品をテストするか、サービス部門で製品を修理する場合、評価/デバッグ・テスト・ポイントを使用するか、また、現時点で知り得ないリスクをどのように管理するか。

例えば、評価手法として、新しいASIC/FPGAを使った新しいシ ステム・アーキテクチャを評価するため、数多くのプロービング・ テスト・ポイントをもった評価用のプロトタイプを作ることがあ ります。評価用のプロトタイプをフルスピードでテストし、その スピードにおける動作や性能を評価する事がベストです。複雑な 設計では、問題点をすばやく、ピンポイントで見つけるための、 リアルタイム動作の総合的、視覚的な検証が必要になります。評 価用のプロトタイプが正しく機能することがわかり、評価が完了 したならば、最終のプロトタイプでは、テスト・ポイントを減ら して実装することができます。

SDRAMの評価

DRAMの評価とテスト技術は、どのように設計されたかによって異なります。DRAMの設計は、次のようにグループ分けできます:コンピュータ・メモリ・コントローラ・ハブIC、メモリIC、AMB IC、DIMM、コンピュータ・マザーボード、組み込みシステム。どの製品も、異なった評価手法、評価用テスト、評価用テスト機器が必要になります。例えば、メモリICの設計エンジニアは、回路基板の製造については評価しませんが、DIMMの設計エンジニアはDIMM基板を評価します。

メモリ・コントローラは、通常、組み込みシステム設計エンジニアが設計します。これは、特定のプロセッサとユニークな組み込みシステム入出力構成を組み合わせて動作させるための独自な要求があるためです。結果として、設計作業で特に重要となるのは、メモリ・コントローラの設計と、メモリ・コントローラとメモリIC間の回路基板のレイアウト設計となります。設計のこの部分を評価することは、確実な動作のためには非常に重要です。

| 評価 | 項目 | 計測器 |

| 回路基板製造 | シングルエンドの配線インピーダンス差動の配線インピーダンス | TDR(サンプリング・オシロスコープ)TDR(サンプリング・オシロスコープ) |

| トレース長 | TDR(サンプリング・オシロスコープ) | |

| クロストーク | TDT(サンプリング・オシロスコープ) | |

| 電源と信号 | 電源品質、ノイズ、グリッチ、グランド・バウンス | オシロスコープ |

| クロックのシグナル・インテグリティ、立上り/立下り時間スルー・レート、拡散スペクトラム・クロック・プロファイル | オシロスコープ(ジッタ解析ソフト) | |

| コマンド、アドレスとデータの有効ウィンドウ、クロック、ストローブとデータ信号のスキュー | オシロスコープ(ジッタ解析ソフト) | |

| FB-DIMMシリアル信号データの有効ウィンドウ | オシロスコープ(シリアル・データ・コンプライアンス/解析ソフト)シグナル・ゼネレータとFB-DIMMフィクスチャ | |

| プロトコル・シーケンスとタイミング | メモリ・システムの電源投入時の 初期化プロトコルとタイミング | ロジック・アナライザ (SDRAMサポート・パッケージ) |

| SDRAMモード・レジスタの動作 | ロジック・アナライザ(SDRAMサポート・パッケージ) | |

| SDRAMコマンド・プロトコルとタイミング | ロジック・アナライザ(SDRAMサポート・パッケージ) | |

| リード/ライト・データの有効ウィンドウ | ロジック・アナライザ(SDRAMサポート・パッケージ) | |

| リフレッシュ動作 | ロジック・アナライザ(SDRAMサポート・パッケージ) | |

| メモリ・チャンネル・トラフィック | ロジック・アナライザ(FB-DIMM/SDRAMサポート・パッケージ) |

表9:評価項目とテスト機器

DRAMの評価、テストには、サンプリング・オシロスコープ、オシロスコープ、ロジック・アナライザ、プローブ、テスト・フィクスチャ、解析ソフトウェア、コンプライアンス・ソフトウェアなど、広範囲な計測器が必要になります(表9参照)。テスト機器では、被測定回路に負荷を与えないプロービング、正確なアクイジション、電気信号とプロトコル・レイヤのシステムの視覚化が必要になります。設計エンジニアにとっては、メモリ動作の短時間の評価、強力な解析能力が必要になります。

コンピュータ・システムや組み込みシステムをロジック・アナラ イザで観測することで、強力な評価/デバッグが可能になります。 ロジック・アナライザでは、プロセッサのバス動作、メモリ動作、 入出力動作のトレースと相互の関連付けが可能になります。ロジッ ク・アナライザでは、システム全体が視覚的に表示でき、リアルタイムなシステム動作を評価できます。さらに、オシロスコープ とロジック・アナライザの統合されたプロービング、トリガ、表 示機能により、ソフトウェア・リスト、プロトコル・リスト、デ ジタル波形、アナログ波形などが同じディスプレイで表示できま す。これらにより、強力で、効率の良い解析が可能になります。

当社は、業界をリードするオシロスコープ、真の差動TDR、 Nexus Technology社のメモリ・サポートとロジック・アナラ イザを初めとする幅広いツール・セットを提供し、組み込みシス テム、コンピュータ設計エンジニアのためのメモリ設計の正確な 電気的テストと動作評価がすばやく、正確に行えます。これらの ツール・セットを使用することで、優れた操作性と性能が実現さ れ、組み込みシステムやコンピュータ・メモリ・システムの評価、 デバッグの理想的なソリューションとなります。

用語集

ご参考のため、この入門書では使われていない用語についても記載しています。

AMB(Advanced Memory Buffer/拡張メモリ・バッファ):高速シリアル・クロックの割り当て、フレーム・バウンダリの特定、チャンネル接続の評価など、サウスバウンドとノースバウンド・チャンネルの初期化を行う。

Amplitude(振幅):信号の量、強さを示す大きさ。電気分野では、通常、電圧または電力であらわす。

Analog Signal(アナログ信号):連続的に変化する電圧の信号

ADC(Analog-to-Digital Converter/アナログ・デジタル変換器):電気信号を離散的な2進値に変換するデジタル電気部品

Asynchronous(非同期):同期でないこと。ロジック・アナライザは、自身のサンプリング・クロックで実行する。クロックは独立しており、被測定回路のタイミングには関係ない。非同期は、タイミング・モードの基本。

Attenuation(減衰):一つのポイントから別のポイントへ転送する際に信号振幅が減少すること。

BGA(Ball Grid Array/ボール・グリッド・アレイ):集積回路パッケージの一種。

Bandwidth(周波数帯域):周波数レンジ。通常は、-3dB減衰する周波数をさす。

Bit(ビット):1または0で状態を表す2進数

Byte(バイト):通常8ビットで構成される一つのデジタル情報の単位

CE#(Chip Enable/チップ・イネーブル):デバイスをアクティベートする信号

CS#(Chip Select/チップ・セレクト):デバイスを選択する信号

Clock Rate(クロック・レート):デバイスが基本的な動作を実行する、一秒間あたりの基本サイクル・レート

CAS#(Column Address Select/列アドレス・セレクト):デバイス内の列アドレスを指定する信号

Cursor(カーソル):正確な波形測定のためのオンスクリーン・マーカ。

CRC(Cyclic Redundancy Code/巡回冗長コード):受信、保存、転送されるデータが壊れていないか検出するためのブロック数。CRCを巡回し、転送された元の値と比較することで、レシーバにおいて転送エラーを検出することができる。

dB(Decibel/デシベル):二つの電気信号における、電力の相対的差異を表す単位。二つのレベルの比の常用対数を10倍する。

DUT(Device Under Test/被測定デバイス):計測器によってテストされるデバイス。

Digital Oscilloscope(デジタル・オシロスコープ):測定した電圧をデジタル情報に変換するためのADC(アナログ・デジタル変換器)を使用したオシロスコープの一種。デジタル・ストレージ、デジタル・フォスファ、デジタル・サンプリングの3種類がある。

DPO(Digital Phosphor Oscilloscope/デジタル・フォスファ・オ シロスコープ):波形の保存、自動測定など、従来のデジタル・ オシロスコープの利点を持ちながら、アナログ・オシロスコープ の表示特性を模したデジタル・オシロスコープの一種。DPOで は、並列処理アーキテクチャによって信号をラスタ・タイプの表 示に送ることにより、リアルタイムに輝度階調のある波形表示が 可能になる。DPOでは、振幅、時間および時間に対する振幅の分 布の3次元で表示する。

Digital Sampling Oscilloscope(デジタル・サンプリング・オシロスコープ):等価時間サンプリングを採用しているデジタル・オシロスコープの一種で、オシロスコープのサンプル・レートよりも高速な信号成分を持った信号を正確に測定するのに適している。

Digital Signal(デジタル信号):電圧が離散的な2進値で表される信号。

DSO(Digital Storage Oscilloscope/デジタル・ストレージ・オシロスコープ):デジタル・サンプリング(アナログ・デジタル変換器を使用)によって信号を取り込むデジタル・オシロスコープのこと。アクイジション、ユーザ・インタフェース、ラスタ表示などをシリアル処理アーキテクチャで実行する。

Digitize(デジタイズ):アナログ・デジタル変換器によって実行されるプロセスで、水平軸システムにより離散的な時間でサンプリングし、そのポイントでの電圧を、サンプル・ポイントと呼ばれるデジタル値に変換する。

DDR(Double Data Rate/ダブル・データ・レート):クロックの2倍のデータ・レートでコマンドを読み書きする。

DIMM(Dual Inline Memory Module):PCで使用されるDRAM用に広く採用されているパッケージ規格。

DRAM(Dynamic Random Access Memory/ダイナミック・ランダム・アクセス・メモリ):メモリの一種で、各データ・ビットを個別のコンデンサによって記憶する。

ECC(Error Correction Code/エラー・コレクション・コード):エラー検出/訂正のための8ビット・コード。

FET(Field Effect Transistor/電界効果トランジスタ):電界によって出力電流を制御するトランジスタ。

FBGA(Fine-pitch Ball Grid Array):集積回路パッケージの一種。

Frequency(周波数):信号が一秒間で繰り返す回数で、Hz(ヘルツ)で表される。1/周期に等しい。

FB-DIMM(Fully Buffered Dual Inline Memory Module):次世代のメモリ・アーキテクチャ。

Gb(Gigabit/ギガビット):10億ビットの情報。

GB(Gigabyte/ギガバイト):10億バイトの情報。

GHz(Gigahertz/ギガヘルツ):10億ヘルツのこと。

GT/s(Gigatransfers per Second):一秒当たり10億のデータ転送。

Glitch(グリッチ):回路で間欠的に発生する高速なエラー

Hz(Hertz/ヘルツ):周波数の単位で、一秒間に一回のサイクル。

iCapture™ Multiplexing(iCapture™マルチプレックシング):一本のロジック・アナライザ・プローブで、デジタル、アナログの両方の同時信号取り込みが可能。

iLink™ Toolset (iLink® ツール・セット):迅速なトラブル検出、トラブルシュートのための、iCapture™、iView、iVerify™などを含んだツール・セット。

I/O(Input/Output):デバイスへの入出力信号。

IC(Integrated Circuit/集積回路):エッチング、刻印された部品、相互接続の集合セット。

Interleave(インターリーブ):一定の間隔で交互に配置すること。

iVerify™ Analysis(iVerify™解析):複数チャンネルのバス解析と、オシロスコープで作成されたアイパターンによる評価テストが可能になります。

iView™ Display(iView™表示):ロジック・アナライザの表示上で、ロジック・アナライザとオシロスコープによる測定を、時間相関をとりながら表示します。

JEDEC( Joint Electron Device Engineering Council): EIA(Electronic Industries Alliance)の半導体技術標準化団体であり、電子部品に関する業界団体。

kHz(Kilohertz/キロヘルツ):1000Hzのこと。

Latency(レイテンシ):送信から受信までに要する時間。例として、DQピンでデータが利用できる場合、最初のステップから三番目のステップのリード・サイクルに要する時間。

Loading(負荷):プローブとオシロスコープによる意図しない影響であり、被測定回路に接続することで信号を劣化させる。

Logic Analyzer(ロジック・アナライザ):時間に対するデジタル信号の論理状態を観測するための計測器。デジタル・データを解析し、リアルタイムなソフトウェア実行、データ・フロー、ステート・シーケンスなどが表示できる。

MagniVu® Acquisition(MagniVu® アクイジション):当社ロジック・アナライザの核となる、独自の高分解能サンプリング・アーキテクチャ。トリガ・ポイント周辺の信号を高分解能でダイナミックに記録できる。

Mb(Megabit/メガビット):100万ビットの情報。

MB(Megabyte/メガバイト):100万バイトの情報。

MHz(Megahertz/メガヘルツ):100万ヘルツ

MS/s(Megasamples per second/メガサンプル/秒):一秒間に100万サンプルのサンプル・レート

MT/s(Megatransfers per second/メガトランスファ/秒):一秒間に100万のデータ転送。

Memory Cycle Time(メモリ・サイクル・タイム):リード・サイクルの最初のステップから最後のステップを完了するまでの時間

μs(Microsecond/マイクロセカンド):0.000001秒。

ms(Millisecond/ミリセカンド):0.001秒。

Mini-DIMM( Miniature Dual Inline Memory Module): SODIMMと似ており、通常、シングル・ボード・コンピュータで使用される。

Motherboard(マザーボード):コンピュータのメイン・システム回路基板であり、プロセッサ、メモリ・コントローラ、ハードディスク・コントローラ、入出力インタフェース・チップなどを含む。DIMMやビデオ・カードなどの回路基板は、マザーボードに接続される。

Nanosecond(ns/ナノセカンド):0.000000001秒。

Noise(ノイズ):回路で発生する予期しない電圧または電流。

Oscilloscope(オシロスコープ):時間に対する電圧の変化を表示する計測器。「オシロスコープ」という名前は、発振(Oscillate)電圧を測定したことから由来している。

OE#(Output Enable/出力イネーブル):デバイスの出力をアクティベートする。

Period(周期):波形の1サイクルが完了する時間。(1/周波数)に等しい。

Pre-trigger Viewing(プリトリガ観測):トリガ・イベント前の信号を捉えるデジタル計測器の機能。トリガ以前の観測時間は設定可能。

Precharge(プリチャージ):適切な電荷をキャパシタに蓄えられるためのDRAMのアクセス・サイクルのステップ

Probe(プローブ):計測器の入力デバイスであり、通常は、回路要素と電気的な接点を持つための、先端の尖った金属チップとグランド基準に接続するためのリード、そして、信号とグランドを計測器に導くためのケーブルで構成されている。

Pluse(パルス):高速な立上りエッジと立下りエッジを持った波形の形状をさす。

Pluse Train(パルス列):パルスが連なった集合。

Pluse Width(パルス幅):パルスがローからハイになり、再びローになるまでの時間。全電圧の50%点間を測定する。

Ramps(ランプ):一定のレートで変化する正弦波の電圧レベル間の遷移。

RAM(Random Access Memory):任意の順序で情報がアクセスされるメモリ・デバイス。

ReadCycle(リード・サイクル):デバイスから読み出すため周期的に繰り返されるイベント・シーケンス。

Record Length(レコード長):信号レコードを作成するための波形ポイント数

Refresh(リフレッシュ):チップをリチャージするために新しい電子パルスを送って電荷の損失を防ぐ。

RDIMM(Registered Dual Inline Memory Module):RDIMMSDRAMクロック、コマンド信号、アドレス信号をバッファリングすることで、ツリー・スタブ・アーキテクチャの問題を軽減する。

Rise Time(立上り時間):パルスのトレーリング・エッジがローからハイまで要する時間。通常は10~90%で測定する。

Rise Time(立上り時間):パルスのトレーリング・エッジがローからハイまで要する時間。通常は10~90%で測定する。

RAS#(Row Address Select/行アドレス・セレクト):デバイス内の対象とする行アドレスを指定する。

Sample Point(サンプル・ポイント):波形ポイントを計算するために使用されるADCからの生データ。

Sample Rate(サンプル・レート):S/s(サンプル数/秒)で表され、デジタル機器がどの程度の頻度で信号をサンプリングするかを表す。

Sampling(サンプリング):計測器で入力信号を保存、プロセス、表示するために、離散的な電気の値に変換すること。

SPD(Serial Presence Detect):独立した、電気的に消去/プログラムが可能なリード・オンリ・メモリ(EEPROM)により、モジュール密度、タイミング、パフォーマンスのパラメータを格納する。

Signal Integrity(シグナル・インテグリティ):デジタル信号の高速化によって生じるリンギングやクロストーク、グランド・バウンスなどのノイズがいかに抑えられているか、すなわちデジタル信号の波形品質のこと。

Signal Source(信号ソース):回路に信号を入力するために使用されるテスト機器。回路からの出力は計測器に取り込まれる。シグナル・ゼネレータとも呼ばれる。

SO-DIMM(Small Outline Dual Inline Memory Module):ノートPCなどのスペースが限られている場合に使用される小型のDIMM。

Synchronous(同期):ロジック・アナライザのステート・アクイジションは同期で行われる。これは、クロック信号を外部(通常はDUT)から取り込むためである。これにより2つのシステムが同期し、ロジック・アナライザはDUTがアクティブの場合にのみ取り込む。これがステート・モード。

SDRAM(Synchronous Dynamic Random Access Memory):DRAMの動作を他のコンピュータ・システムと同期させ、CE#、RAS#、CAS#、WE#エッジ・トランジションのシーケンスによるメモリ動作モードを機種ごとに定義しなくてすむようにしたメモリ。

SUT(System Under Test/被測定システム):計測器によって測定されるシステム

TDR(Time Domain Reflectometry):PCボード上のケーブル、コネクタ、マイクロストリップなどのインピーダンスや伝送ラインによる変化を評価する方法。

Trigger(トリガ):測定器の水平掃引の基準となる回路

Trigger Holdoff(トリガ・ホールドオフ):有効なトリガの後の、計測器がトリガしない期間を設定する機能。

Trigger Level(トリガ・レベル):トリガのソース信号がそのレベルに達することで水平掃引を開始する電圧レベル。

UDIMM(Unregistered Dual Inline Memory Module):DIMMの最初の実装。UDIMMには、DDR、DDR2、DDR3信号をバッファリングしていません。

VLP-DIMM(Very Low Profile Dual Inline Memory Module):DIMMに比べて高さの低いDIMMであり、ブレード・サーバなどで使用される。

V(Volt/ボルト):電位差の単位。

Voltage(電圧):2点間の電位差をボルト(V)で表したもの。

Wave(波形):時間に対して繰り返されるパターンの総称。一般的なタイプとして、正弦波、方形波、のこぎり波、三角波、ステップ、パルス、周期、非周期、同期、非同期などがある。

WE#(Write Enable/書き込みイネーブル):デバイスに対する書き込みをイネーブルにする。