Spread Spectrum Clocking (SSC) is a highly effective technique utilized to reduce electromagnetic interference or EMI. PCI Express 5.0 System designers use this tool to reduce the adverse effects on adjacent circuits and to pass FCC or other regulatory body requirements for EMI emissions. Manifestations of EMI can result in performance degradation and loss of digital information. Validation of your PCIe 5.0 system with SSC is strongly recommended to ensure optimal performance of the link once the system under test is delivered to customers.

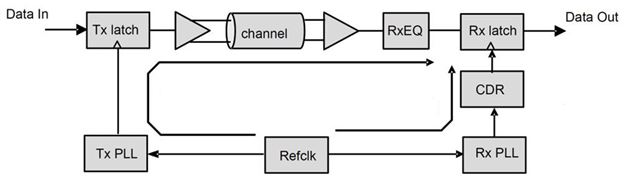

The common clock architecture is required for Card Electromechanical (CEM) devices, where a single 100 MHz refclk is shared between the upstream and downstream facing ports. Latest drafts of the Physical Layer Test specification (also known as the Compliance Test Spec) require PCIe 5.0 systems to be certified with SSC enabled when the system will operate with SSC once deployed. Engineers working on pre-compliance are advised to test both with and without SSC to ensure the device will pass the physical layer tests once the PCI-SIG 5.0 certification program is active.

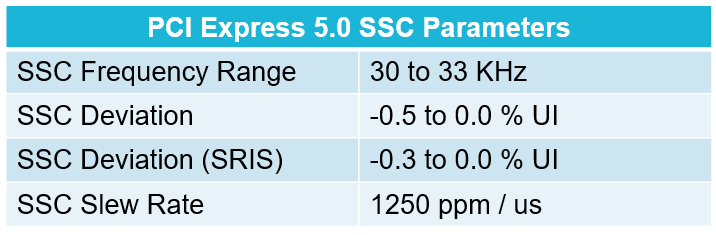

The table shows the specific electrical requirements of SSC for PCIe 5.0 operating at a data rate of 32 GT/s. Note that devices implementing the CEM specification require 5000 ppm of SSC deviation. This is relaxed to 3000 ppm for non-CEM compliant devices taking advantage of separate refclks with SSC. Not all Receiver test and measurement equipment are capable of meeting this 5000ppm SSC requirement including the Bit Error Rate Tester’s (BERT) clock recovery and other error detector capabilities. The automated PCIe 5.0 Receiver test solution from Anritsu and Tektronix offers comprehensive coverage when testing 32 GT/s capable devices with the 5000 ppm SSC requirement. Allowing you to confidently bring your 5.0 device to a PCI-SIG workshop knowing your pre-compliance testing aligns with the standard body requirements.

For more information on PCI Express Gen 5 and the challenges of receiver compliance and validation, check out the on-demand webinar. You’ll also see a demo showing the fully-automated Tektronix - Anritsu solution specifically looking at the aspect of calibrating the stressed-eye.