DIESER ANWENDUNGSHINWEIS

- Bietet eine kurze Orientierung über die physikalische Schicht und die Paketstrukturen von I2C und SPI, mit dem Ziel, genügend Einzelheiten zu liefern, um bei der Fehlersuche zu unterstützen

- Erklärt die Einrichtung der Dekodierung auf einem Oszilloskop, das mit I2C- und SPI-Dekodierung ausgestattet ist

- Erklärt, wie serielle Busdaten auf einem mit I2C- und SPI-Dekodierung ausgestatteten Oszilloskop ausgewertet werden

- Erklärt, welche Trigger- und Suchoptionen auf einem Oszilloskop mit I2C- und SPI-Dekodierung verfügbar sind

Mit der optionalen seriellen Trigger- und Analysefunktion werden die Oszilloskope von Tektronix zu leistungsstarken Tools für Entwickler von eingebetteten Systemen, die auf Basis von I2C- und SPI-Bussen funktionieren. In diesem Anwendungshinweis wird das MSO der Serie 5 zur Demonstration der Dekodierung und Triggerung von seriellen I2C- und SPI-Bussen verwendet.

Die MSO-Oszilloskope der Serien 2, 4, 5 und 6 von Tektronix unterstützen I2C- und SPI-Triggerung und -Analyse. Der Betrieb all dieser Geräte ist praktisch identisch mit dem in diesem Anwendungshinweis verwendeten MSO der Serie 5. Weitere Informationen finden Sie im Leitfaden zur Oszilloskop-Auswahl.

Einleitung

Die meisten Mikrocontroller-basierten Designs verwenden I2C oder SPI oder beides, um zwischen Controllern und zwischen Controllern und Peripheriechips zu kommunizieren. Bei der Fehlersuche kann es entscheidend sein, zu sehen, was in einem eingebetteten System passiert, wenn ein Chip ein bestimmtes I2C- oder SPI-Paket sendet. Viele Chips, die relativ langsame Parameter verwalten, wie beispielsweise Temperatursensoren, Motorsteuerungen, Benutzerschnittstellen oder Energieverwaltung, verwenden diese Busse als primäres Mittel zur Kommunikation mit dem Rest des Systems. Andere Chips mit höherer Geschwindigkeit, wie zum Beispiel Kommunikations-ICs, Taktgeber und ADCs, werden oft über diese Busse konfiguriert. Um beispielsweise ein Problem mit einem Lüfter nach dem Einschalten zu beheben, kann es hilfreich sein, sich das Timing und die Struktur der SPI-Befehle anzusehen, die an den Lüftersteuerungs-IC gesendet werden, sowie das Ansteuerungssignal für den Lüfter und die Stromversorgung.

I2C- und SPI-Busse sind eindeutig definiert und relativ robust, aber sie können dennoch durch Rauschen, Platinenlayout, Reset-Probleme und durch feine Unterschiede in der Implementierung beeinträchtigt werden. Dies kann in einigen Fällen zu Busfehlern und Blockaden führen. Mit Oszilloskopen, die über eine Dekodierfunktion verfügen, können Sie sowohl die Busdaten als auch den Zustand der Bussignale gleichzeitig einsehen.

I2C

I2C, oder „I Quadrat C“, steht für Inter-Integrated Circuit. Das Konzept wurde ursprünglich von Philips in den frühen 1980er-Jahren entwickelt, um eine kostengünstige Möglichkeit zur Verbindung von Controllern mit Peripheriechips zu schaffen. Seitdem hat es sich zu einem weltweiten Standard für die Kommunikation zwischen Geräten in eingebetteten Systemen entwickelt. Dieses einfache Zweidraht-Design hat seinen Weg in eine Vielzahl von Chips wie E/A, A/Ds, D/As, Temperatursensoren, Mikrocontroller und Mikroprozessoren zahlreicher führender Chiphersteller gefunden, darunter: Analog Devices, Atmel, Infineon, Cypress, Intel, Maxim, NXP, Silicon Labs, ST Microelectronics, Texas Instruments, und weitere.

So funktioniert der Komplettschutzplan

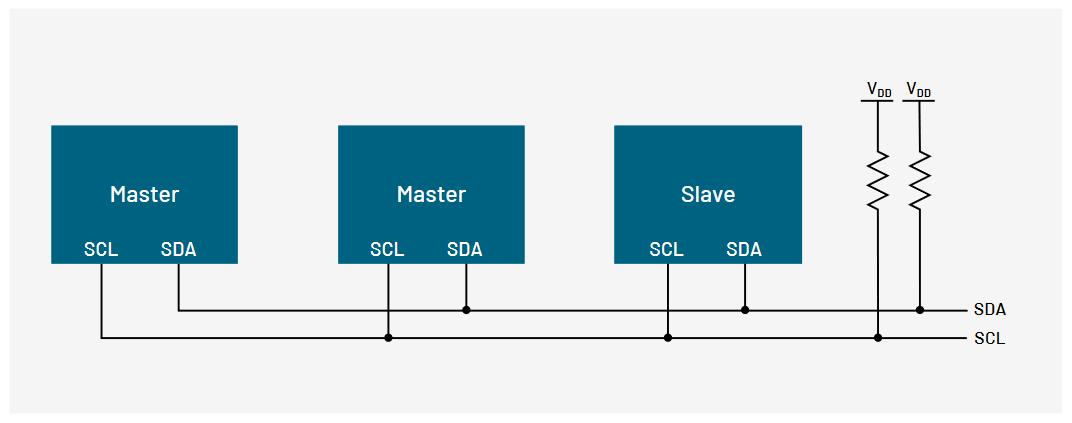

Die physikalische Zweidrahtschnittstelle des I2C besteht aus bidirektionalen seriellen Takt- (SCL) und Datenleitungen (SDA). I2C unterstützt mehrere Master und Slaves auf dem Bus, wobei jedoch nur ein Master gleichzeitig aktiv sein kann. Jedes I2C-Gerät kann an den Bus angeschlossen werden, wodurch jedes Master-Gerät Informationen mit einem Slave-Gerät austauschen kann. Alle Geräte werden anhand einer eindeutigen Adresse erkannt. Ein Gerät kann je nach seiner Funktion entweder als Sender oder als Empfänger arbeiten. Es werden drei Bitraten unterstützt: 100 KB/s (Standardmodus), 400 KB/s (schneller Modus) und 3,4 Mb/s (Hochgeschwindigkeitsmodus). Die maximale Anzahl von Geräten wird durch eine maximale Kapazität von 400 pF bestimmt oder etwa 20 bis 30 Geräten.

| Start | Adresse | R/W | ACK | DATA0 | ACK0 | Daten 1 | ACK1 | ... | DATAN | ACKN | Stopp |

| 7- oder 10-Bit | 1 Bit | 1 Bit | 8 Bit | 1 Bit | 8 Bit | 1 Bit | 1 Bit | 8 Bit | 1 Bit |

Der I2C-Standard definiert das folgende Format:

- Start – zeigt an, dass das Gerät die Kontrolle über den Bus übernimmt und eine Nachricht folgen wird.

- Adresse – eine 7- oder 10-Bit-Zahl, die die Adresse des Geräts darstellt, von dem entweder gelesen oder auf das geschrieben wird. Ursprünglich wurden bei I2C nur 7-Bit-Adressen verwendet, aber inzwischen ist auch eine 10-Bit-Adressierung möglich. Drei

- R/W Bit – ein Bit, das anzeigt, ob die Daten vom Gerät gelesen oder in das Gerät geschrieben werden.

- Ack – ein Bit vom Slave-Gerät, das die Aktionen des Masters bestätigt. Normalerweise gibt es für jedes Adress- und Datenbyte eine Bestätigung, aber nicht immer.

- Daten – eine ganzzahlige Anzahl von Bytes, die aus dem Gerät gelesen oder auf das Gerät geschrieben wurden.

- Stop – zeigt an, dass die Nachricht vollständig ist und der Master den Bus freigegeben hat.

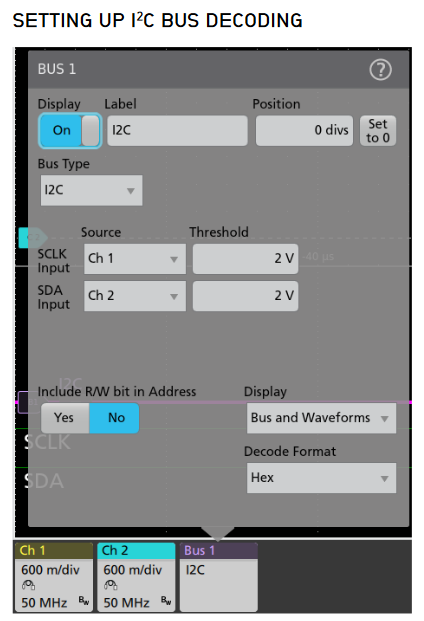

Es gibt zwei Möglichkeiten, I2C-Adressen für die Dekodierung zu gruppieren: in 7-Bit plus ein Lese- oder Schreibbit (R/W) und in 8-Bit (ein Byte), wobei das R/W-Bit als Teil der Adresse enthalten ist. Das 7-Bit-Adressschema ist der spezifizierte I2C-Standard, dem die Entwickler von Firmware und Software folgen. Viele andere Ingenieure verwenden jedoch das 8-Bit-Adressschema. Die Oszilloskope von Tektronix können Daten in beiden Varianten dekodieren.

EINRICHTUNG DER I2C-BUS-DEKODIERUNG

Bei Tektronix-Oszilloskopen können Sie durch das Drücken der Bus-Taste auf der Vorderseite die Eingänge des Oszilloskops als Bus definieren. Indem Sie einfach festlegen, auf welchen Kanälen Takt und Daten liegen, zusammen mit den digitalen Schwellenwerten, die zur Bestimmung von logischen Einsen und Nullen verwendet werden, ermöglichen Sie dem Oszilloskop, das über den Bus übertragene Protokoll zu verstehen.

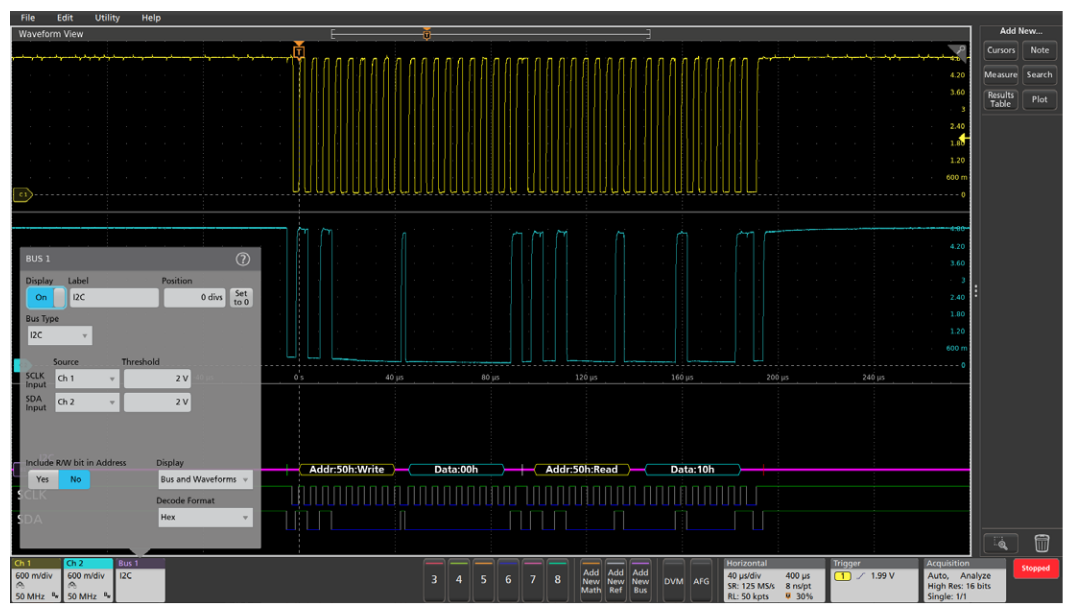

AUSWERTUNG DES I2C-BUSSES

Die zeitkorrelierte Wellenform- und Busdekodierungsanzeige ist ein vertrautes und nützliches Format für viele Hardware-Ingenieure. Die dekodierte Bus-Wellenform zeigt die Elemente einer I2C-Nachricht an.

| I2C-BUS-ELEMENT | ANGEZEIGT DURCH |

| Starts Wiederholte Starts treten auf, wenn ein weiterer Start angezeigt wird, ohne dass zuvor ein Stopp erfolgt ist. |

|

| Adressen [W] zeigt einen Schreibvorgang und [R] einen Lesevorgang an, wobei die Adresswerte entweder in hexadezimaler oder binärer Form angezeigt werden können. |

|

| Daten Datenwerte können entweder in hexadezimaler oder binärer Form angezeigt werden. |

|

| Fehlende Acks |

|

| Stops |

|

Für Firmware-Ingenieure könnte das Format der Ergebnistabelle nützlicher sein. Diese mit einem Zeitstempel versehene Anzeige der Busaktivität kann leicht mit Software-Auflistungen verglichen werden und ermöglicht eine einfache Berechnung der Ausführungsgeschwindigkeit.

Die Ergebnistabelle bietet auch eine Verknüpfung mit den Wellenformanzeigen. Sie können auf eine Zeile in der tabellarischen Anzeige tippen und das Oszilloskop zoomt automatisch auf die entsprechenden Bussignale und die daraus resultierende dekodierte Bussignalform, die im unteren Bereich des Bildschirms angezeigt wird.

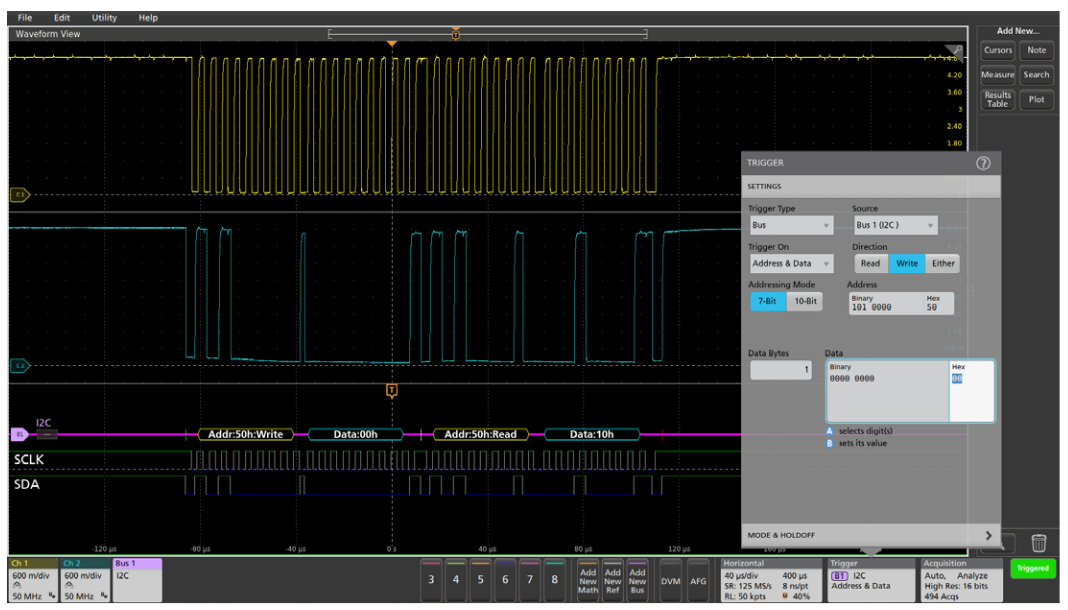

TRIGGERUNG AUF DEM I2C-BUS

Bei der Fehlersuche in einem System, das auf einem oder mehreren seriellen Bussen basiert, ist eine der wichtigsten Funktionen des Oszilloskops das Isolieren und Erfassen bestimmter Ereignisse mit einem Bustrigger. Wenn der Bustrigger richtig eingestellt ist, erfasst das Oszilloskop alle Eingangssignale und ein bestimmtes Busereignis wird am Triggerpunkt positioniert. In diesem Beispiel wird die Triggerung auf Adresse 0x50 und Daten 0x00 demonstriert.

| Triggern auf | BESCHREIBUNG |

| Start | Triggert, wenn SDA nach unten geht, während SCL hoch ist. |

| Wiederholter Start | Triggert, wenn eine Startbedingung ohne vorherige Stoppbedingung auftritt. Dies ist normalerweise der Fall, wenn ein Master mehrere Nachrichten sendet, ohne den Bus freizugeben. |

| Stopp | Triggert, wenn SDA nach oben geht, während SCL hoch ist. |

| Fehl. Bestät. | Slaves sind oft so konfiguriert, dass sie nach jedem Byte von Adresse und Daten eine Bestätigung senden. Das Oszilloskop kann in den Fällen triggern, in denen der Slave das Acknowledge-Bit nicht generiert. |

| Adresse | Triggert auf eine benutzerdefinierte Adresse oder eine der vorprogrammierten Spezialadressen wie General Call, Start Byte, HS-Mode, EEPROM oder CBUS. Die Adressierung kann entweder 7 oder 10 Bit betragen und wird in Binär- oder Hexadezimalwerten eingegeben. |

| Daten | Triggert auf mehrere Bytes von benutzerdefinierten Datenwerten, die entweder binär oder hexadezimal eingegeben werden. |

| Adresse und Daten | Dies ermöglicht es Ihnen, sowohl Adress- und Datenwerte einzugeben als auch Lesen vs. Schreiben, um das genaue gewünschte Ereignis zu erfassen. |

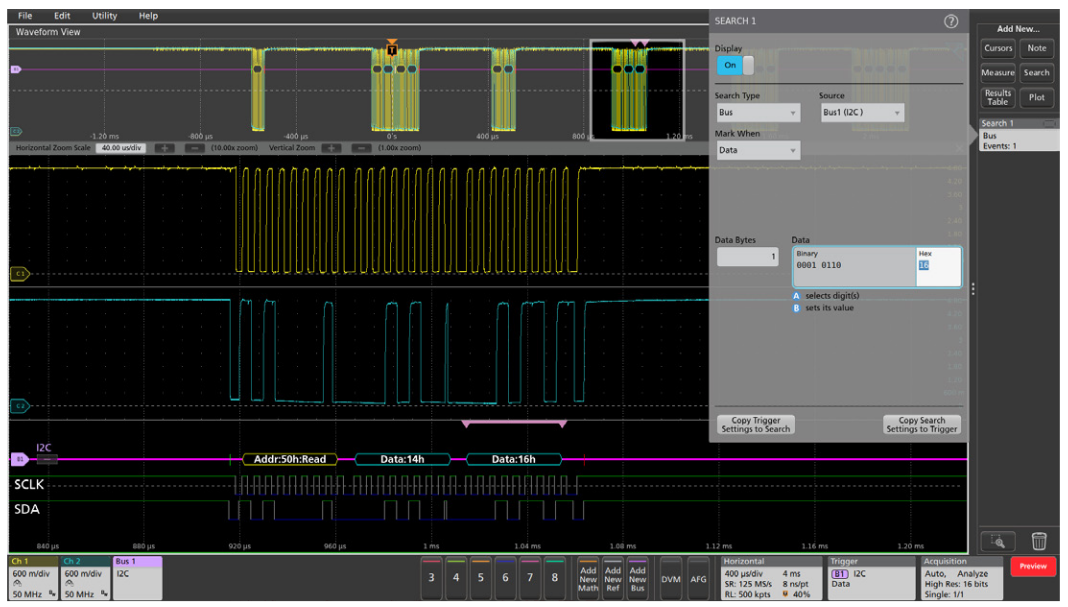

DURCHSUCHEN DES I2C-BUSSES

Mit einem Tektronix-Oszilloskop können Sie den automatischen Wave Inspector verwenden, um alle Busereignisse zu finden, die einem Suchkriterium entsprechen, und um festzustellen, wie viele davon aufgetreten sind. Das Setup ist ähnlich wie das Bus-Trigger-Setup und ermöglicht es dem Oszilloskop, alle angegebenen Bus-Ereignisse zu finden und zu markieren. In diesem Beispiel sucht die automatische Suche nach dem Datenwert 0x16. Dieser Datenwert kommt nur einmal in den erfassten Wellenformen vor, und die Position des seriellen Datenpakets wird mit dem pinkfarbenen Klammersymbol angezeigt.

SPI

Der Serial Peripheral Interface Bus (SPI) wurde ursprünglich von Motorola in den späten 1980er-Jahren für die Mikrocontroller der 68000er-Serie entwickelt. Aufgrund der Einfachheit und Beliebtheit des Busses haben viele andere Hersteller den Standard im Laufe der Jahre übernommen. Heute ist er in einer Vielzahl von Komponenten zu finden, die üblicherweise bei der Entwicklung eingebetteter Systeme verwendet werden. SPI wird hauptsächlich zwischen Mikrocontrollern und ihren unmittelbaren Peripheriegeräten verwendet. Es wird häufig in Mobiltelefonen und anderen mobilen Geräten verwendet, um Daten zwischen der CPU, der Tastatur, dem Bildschirm und den Speicherchips zu übertragen.

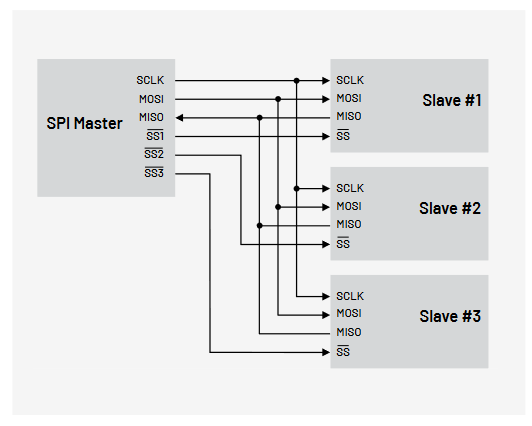

So funktioniert der Komplettschutzplan

Der SPI-Bus ist ein serieller 4-Draht-Kommunikationsbus (Master/Slave). Die vier Signale sind Takt (SCLK), Master-Ausgang/Slave-Eingang (MOSI), Master-Eingang/Slave-Ausgang (MISO) und Slave Select (SS). Wenn zwei Geräte miteinander kommunizieren, wird eines als „Master“ und das andere als „Slave“ bezeichnet. Der Master steuert den seriellen Takt. Die Daten werden gleichzeitig gesendet und empfangen, wodurch es sich um ein Vollduplex-Protokoll handelt.

Anstelle von eindeutigen Adressen für jedes Gerät auf dem Bus verwendet SPI die SS-Leitung, um festzulegen, an welches oder von welchem Gerät Daten übertragen werden. Daher benötigt jedes einzelne Gerät am Bus sein eigenes SS-Signal vom Master. Wenn es 3 Slave-Geräte gibt, gibt es 3 SS-Signale vom Master, eines an jeden Slave.

SPI kann auch so verdrahtet werden, dass die Slave-Geräte in Reihe geschaltet sind, wobei jedes Gerät nacheinander eine Funktion ausführt und dann die Ergebnisse an den Master zurücksendet (was zur Überprüfung der Integrität des Datenpfads verwendet werden kann).

In einigen Fällen, in denen eine Kommunikation vom Slave zurück zum Master nicht erforderlich ist, kann das MISO-Signal ganz weggelassen werden. In anderen Fällen gibt es nur ein Master- und ein Slave-Gerät und das SS-Signal ist mit der Masse verbunden. Dies wird gewöhnlich als 2-Draht-SPI bezeichnet.

Bei einer SPI-Datenübertragung wird ein 8-Bit-Datenwort über MOSI hinausgeschoben, während ein anderes 8-Bit-Datenwort über MISO hereingeschoben wird. Dies kann als ein zirkuläres 16-Bit-Schieberegister betrachtet werden. Bei einer Übertragung wird dieses 16-Bit-Schieberegister um 8 Positionen verschoben, wodurch die 8-Bit-Daten zwischen den Master- und Slave-Geräten ausgetauscht werden. Ein Paar von Registern, die Taktpolarität (CPOL) und die Taktphase (CPHA), bestimmen die Flanken des Takts, an denen die Daten übertragen werden. Jedes Register hat zwei mögliche Zustände, was vier mögliche Kombinationen zulässt, die alle nicht miteinander kompatibel sind. Ein Master/Slave-Paar muss also die gleichen Parameterwerte verwenden, um miteinander zu kommunizieren. Wenn mehrere Slaves in unterschiedlichen Konfigurationen verwendet werden, muss sich der Master jedes Mal neu konfigurieren, wenn er mit einem anderen Slave kommunizieren muss.

EINRICHTUNG DER SPI-BUS-DEKODIERUNG

In diesem Beispiel werden die SPI-Signale mit passiven Tastköpfen an den analogen Kanälen (Kanal 1, Kanal 2 und Kanal 3) des Oszilloskops erfasst. Für die Busdekodierung können auch digitale Kanäle verwendet werden. Mit dem Bus-Konfigurationsmenü können Sie einen SPI-Bus definieren, indem Sie angeben, welche Kanäle mit den Takt-, Daten- und Slave-Auswahlsignalen, den Schwellenwerten, Polaritäten und der Wortgröße verbunden sind.

AUSWERTUNG DES SPI-BUSSES

Durch das Einstellen des Anzeigemodus auf Bus und Wellenformen kann die digitale Interpretation (Vergleich des analogen Signals mit der entsprechenden Schwellenspannung) jedes der Eingangssignale schnell überprüft werden. Diese digitalen Signale (grün ist high und blau ist low) werden dann gemäß dem SPI-Protokoll ausgewertet. Wenn das Oszilloskop richtig eingestellt ist, kann es die dekodierten Ergebnisse anzeigen.

| SPI-BUS-ELEMENT | ANGEZEIGT DURCH |

| Starts Wiederholte Starts treten auf, wenn ein weiterer Start angezeigt wird, ohne dass zuvor ein Stopp erfolgt ist. |

|

| Daten Datenwerte können entweder in hexadezimaler oder binärer Form angezeigt werden. |

|

| Stops |

|

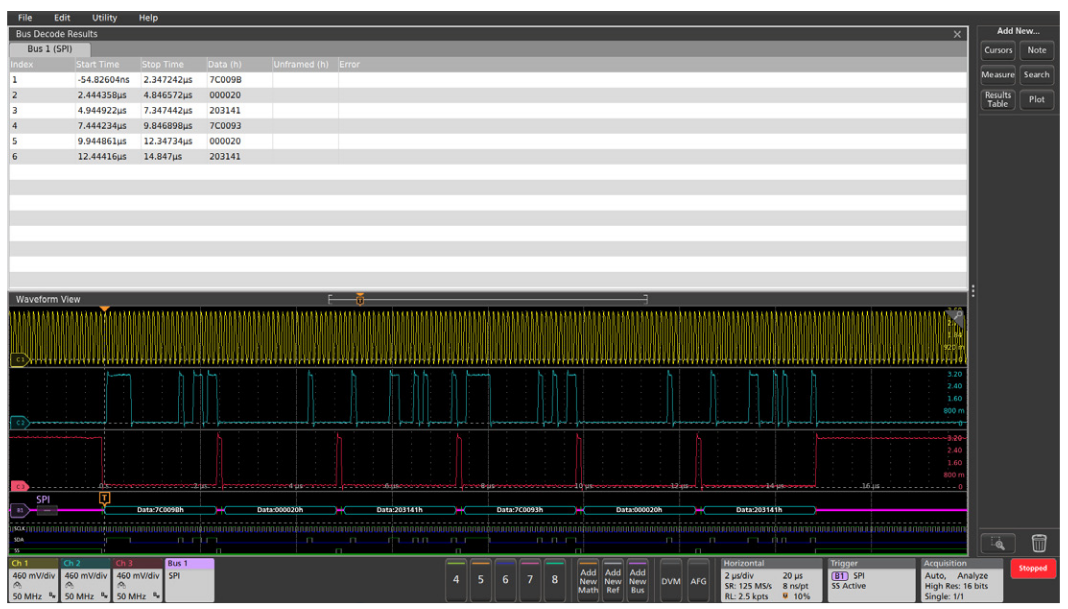

Nehmen wir ein Beispielsystem mit Daisy-Chain-SPI-Architektur. Dieses Subsystem steuert einen spannungsgesteuerten Oszillator (VCO), der den HF-Takt für das übrige System liefert. Der VCO wird von der Haupt-CPU initialisiert, indem sechs 24-Bit-Wörter in den VCO geschrieben werden. Die Signale scheinen die elektrischen Spezifikationen für SPI zu erfüllen, aber der VCO erzeugt nicht die richtige Frequenz.

Die Ergebnistabellenansicht kann verwendet werden, um die VCO-Initialisierung zu untersuchen. Das Oszilloskop kann so eingestellt werden, dass es bei dem aktiven SPI-Slave-Auswahlsignal triggert. Wenn das System hochgefahren wird, erfasst das Oszilloskop die Initialisierungssequenz und zeigt diese an.

TRIGGERUNG AUF DEM SPI-BUS

Im oben genannten Beispiel haben wir einen einfachen SS-Aktiv-Trigger verwendet. Die vollständigen SPI-Trigger-Funktionen der Tektronix-Oszilloskope umfassen die folgenden Typen:

| Triggern auf | BESCHREIBUNG |

| SS\naktiv | Triggert, wenn die Slave-SelectLeitung für ein Slave-Gerät den Zustand „True“ erreicht (3-Draht-Modus). |

| Framebeginn | Triggert zu Beginn eines Frames, wenn die Taktleerlaufzeit zur Festlegung des Frame-Timings verwendet wird (2-Draht-Modus). |

| Daten | Triggerung auf ein Byte oder mehrere Bytes von benutzerdefinierten Daten (MOSI oder MISO). (Die Modelle der Serien 4000/3000/2000 können auf bis zu 16 Byte MOSI- und MISO-Daten triggern). |

Diese Trigger ermöglichen es Ihnen, den Bus-Traffic, an dem Sie interessiert sind, zu isolieren und zu erfassen. Die Dekodierungsfunktion ermöglicht es Ihnen wiederum, den Inhalt jeder Nachricht, die über den Bus übertragen wird, in Ihrer Erfassung sofort einzusehen.

DURCHSUCHEN AUF DEM SPI-BUS

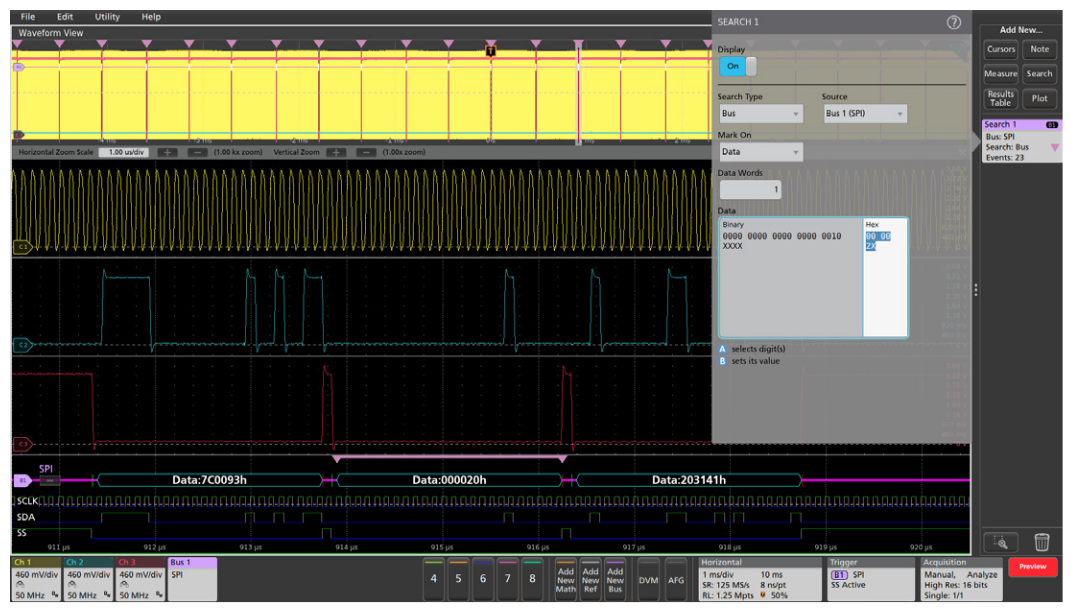

Um alle Bus-Ereignisse zu finden, die ein bestimmtes Suchkriterium erfüllen, kann die automatische Suchfunktion des Wave Inspectors verwendet werden. Das Setup ist ähnlich wie das Bus-Trigger-Setup: Es findet sowie markiert alle angegebenen Bus-Ereignisse. In diesem Beispiel sucht die automatische Suche nach dem 24-Bit-Datenwert 0x00002X. Dieser Datenwert kommt in den erfassten Wellenformen 23 Mal vor. Mit den Navigationspfeiltasten auf der Vorderseite des Geräts können Sie leicht zwischen den markierten Ereignissen navigieren. Die Position eines der angegebenen seriellen Datenpakete wird mit dem pinkfarbenen Klammersymbol am unteren Rand des Bildschirmes angezeigt.

Weitere wertvolle Ressourcen finden Sie unter TEK.COM

Copyright © Tektronix. Alle Rechte vorbehalten. Tektronix-Produkte sind durch erteilte und angemeldete Patente in den USA und anderen Ländern geschützt. Die Informationen in dieser Veröffentlichung ersetzen alle in bisher veröffentlichten Materialien enthaltenen Informationen. Änderungen der Spezifikationen und der Preise vorbehalten. TEKTRONIX und TEK sind eingetragene Marken der Tektronix, Inc. Alle anderen erwähnten Markennamen sind Dienstleistungsmarken, Marken oder eingetragene Marken der betreffenden Firmen.

01/24 55W-61091-2