Свяжитесь с нами

Живой чат с представителями Tektronix. С 9:00 до 17:00 CET

Позвоните нам

С 9:00 до 17:00 CET

Загрузить

Загрузить руководства, технические описания, программное обеспечение и т. д.:

Обратная связь

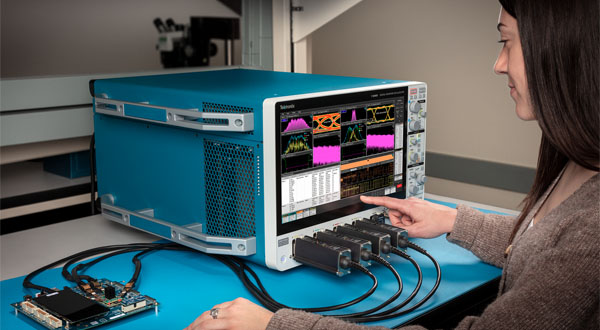

Validating HPC Architectures

Explore how our solutions help you accelerate testing signal and power integrity for bandwidth and data rate scaling as well as validating DDR architectures for high memory bandwidth and granting JEDEC compliance.

AI Data Center Testing Applications

Signal Integrity Measurement and Modeling

Tektronix oscilloscopes, paired with Signal Integrity Modeling (SIM), let you de‑embed measurement path effects, embed real‑world channel conditions, and simulate how signals propagate through complex PCB interconnects — all directly on the instrument. With SIM Advanced (SIMA), you gain powerful equalization modeling — including receiver equalization (CTLE, FFE, DFE) and transmitter pre‑emphasis/de‑emphasis — to open closed eyes and explore design trade‑offs in challenging high‑speed environments.

These tools work hand‑in‑hand with advanced jitter and eye diagram analysis options (e.g., DJA) to break down deterministic and random jitter effects and verify compliance while preserving design margin.

Power Delivery Network (PDN) Validation

AI designs also require rock‑solid power integrity. Delivering hundreds of amps at sub‑1 V rails with minimal noise and transient disturbance is fundamental for deterministic performance. Tektronix oscilloscopes and probes enable PDN impedance and transient characterization, high‑current rail measurement and analysis and correlation of power events with data path behavior.

Achieving Mask Compliance in Tight Timing Windows

Tektronix solutions provide engineers with the ability to measure and verify DDR timing margins directly on high-speed memory interfaces. Using advanced eye diagram and timing analysis, designers can ensure that signals stay within the JEDEC-defined mask while accounting for real-world channel losses, reflections, and interconnect variations. This is critical for maintaining data integrity and system reliability as memory speeds scale.

Transmitter and Receiver Compliance Testing

Tektronix oscilloscopes, combined with automated DDR compliance workflows, simplify the process of validating both DDR transmitters and receivers.

Engineers can run TX compliance tests - to ensure memory modules drive signals within the required voltage and timing windows and RX compliance tests — to verify that memory controllers correctly sample incoming data under worst-case conditions.