與我們聯絡

與 Tek 業務代表即時對談。 上班時間:上午 6:00 - 下午 4:30 (太平洋時間)

請致電

與 Tek 業務代表即時對談。 上班時間:上午 8:30 - 下午 5:30 (太平洋時間)

下載

下載手冊、產品規格表、軟體等等:

意見回饋

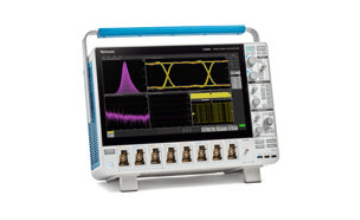

透過進階抖動分析軟體 (選購項目 DJA) ,在各種應用中深入掌握時序細節。DJA 可在 MSO5 系列 B、MSO6 系列 B 及 DPO7 系列 示波器上運行,提供強大的抖動、眼圖與時序分析功能,適用於從低速嵌入式時鐘到高速序列介面的各種應用。無論是串列鏈路、時鐘元件還是 PLL,DJA 都能助您精準找出抖動源頭、加速除錯流程,並充滿信心地完成效能驗證。

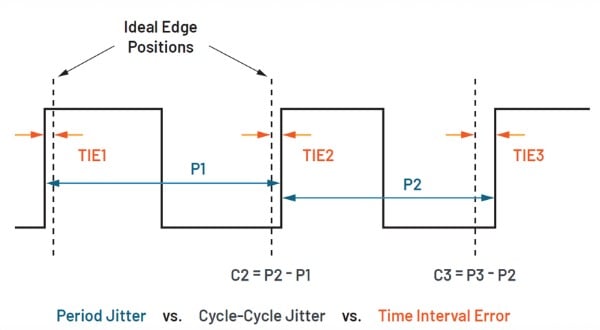

不同的基本抖動量測

驗證與除錯工作流程的抖動分析

抖動是訊號時序中不希望出現的變化,會侵蝕訊號的完整性。在高速系統中,即便細微的時序偏移,也足以導致眼圖崩潰、產生位元錯誤,甚至使設計超出規格範圍。無論是源自電源雜訊、串音、反射,還是時鐘不穩定性,抖動都對您的 USB、PCIe、DDR 和乙太網路設計,進而影響效能與可靠性。

如何識別並解決抖動問題

如果你發現眼圖閉合、資料錯誤或時鐘異常,抖動分析就不是選項,而是必要。Tektronix 提供精準量測工具,如眼圖、TIE 圖與抖動分解分析,協助找出根本原因,並確保時序裕度符合設計要求。

如何對抖動進行分析和除錯:

- 使用具備足夠頻寬的示波器與探棒擷取待測物 DUT 訊號

- 只需點擊幾下,即可使用 DJA 軟體 (選項 DJA) 執行抖動分析

- 進行時鐘恢復設定,以模擬被測系統的行為

- 執行 TIE、眼圖、抖動浴缸圖與頻譜分析。

- 分解總抖動

- 將抖動與可能的根本原因進行關聯分析

- 進行修正並重新測試

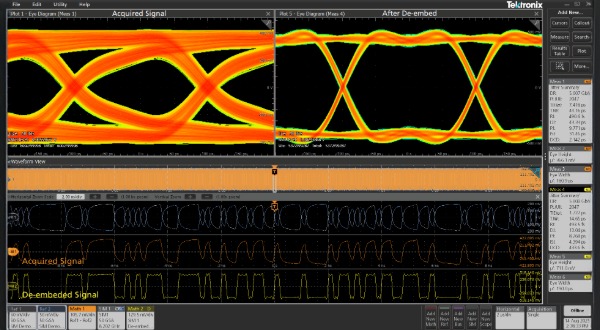

- 使用 SIM 軟體 (選購項目 SIM) 進行解除嵌入、嵌入或等化處理

- 調整等化器 EQ、佈局、電源或元件選擇

- 重新擷取訊號並重新分析,以確認改善效果

- 完整記錄所有內容,以利追溯與符合法規要求

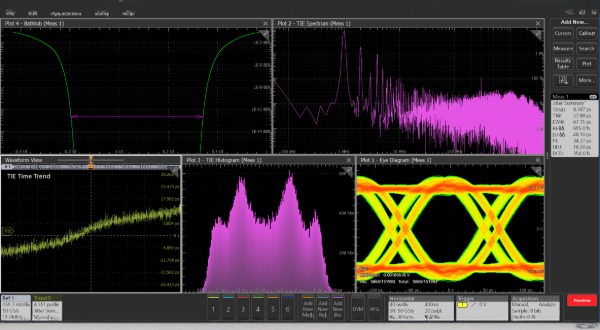

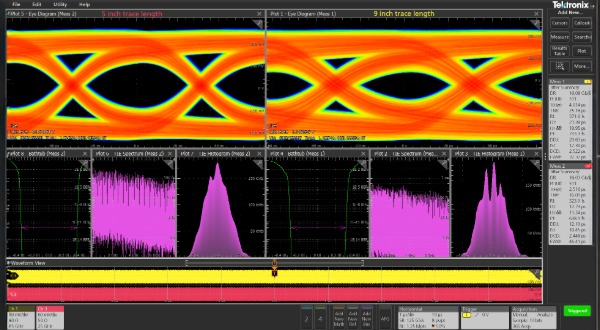

抖動分析顯示,一個 2.5 Gb/s 的連線存在主要的週期性抖動,以約 125 MHz 為主的週期性抖動、來自 ISI 的顯著 DDJ 以及可量測的 DCD。這些現象指出時鐘或電源耦合可能是根本原因。

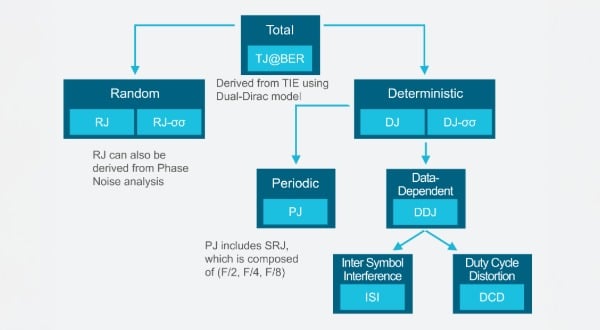

將總抖動拆解為其根本組成部分

抖動分解有助找出根本原因並實施精準對策,例如優化時脈來源、調整等化設定或改善佈局設計。

Tektronix 進階抖動分析 (選項 DJA) 軟體可協助您隔離抖動。只需點擊幾下,即可透過詳細分析以下內容確定總抖動 (TJ):

- 隨機抖動 (RJ):具雜訊特性,且數值無界

- 確定性抖動 (DJ):可預測且數值有界 (例如週期性抖動)

- 以及子元件(PJ、DDJ、ISI、DCD 等)

領先業界的視覺化工具

Tektronix 的進階抖動分析軟體 (選項 DJA) 專為協助您深入了解訊號行為而設計。

- Tektronix 的獨特之處在於支援近乎無限的並行量測與繪圖功能 (每個量測都可設定獨立的時脈回復參數),讓您能快速並排比較均衡策略、容差敏感度或組態變更的影響。

- 多種互動式圖表—包括眼圖、直方圖、浴缸曲線、頻譜圖等—整合於單一介面中,提供更深入的洞察。

- 即時眼圖渲染功能,可同步揭示時序、雜訊與失真現象,並支援使用者可自定義的 PLL 模擬。

- 諸如眼圖高度、眼圖寬度、BER 眼圖、眼圖高/低電平與 Q 因數等眼圖指標,可量化訊號邊界並進行預測性 BER 分析。

- 提供全面的眼圖遮罩測試,包含自動擬合與餘裕視覺化功能,旨在針對廣泛的串列標準進行符合性驗證。

5 吋與 9 吋軌跡的快速並排比較

值得信賴的抖動分析,根據業界標準建立

Tektronix 的抖動、眼圖與時序分析工具,以承襲了定義業界的核心創新精神為設計理念,並具備專利的即時時鐘回復、眼圖繪製與基於頻譜的抖動分解技術作為技術支撐。受 PCI-SIG、USB 和其他領先業界機構的信賴與認證。

Tektronix 的抖動與時序量測技術,採用與業界標準 DPOJET 軟體 相同的成熟演算法,確保長期使用者在一致性、可靠性與延續性上的信賴。

透過參與 Plugfest、相容性研討會及內部比對測試,定期驗證分析結果的關聯性,確保我們的量測結果符合業界方法與預期。