One of the featured sessions during the 2021 Tektronix Innovation Forum was one entitled PCIe Gen5, Gen6 Development and Contrast to IEEE 802.3ck Electrical Ethernet, featuring myself and my colleague, Pavel Zivny. At that session we began by discussing the current status for PCI Express 5.0 at 32 GBd NRZ. Next, we looked ahead to the transition to PCI Express 6.0 at 32 GBd PAM4, reviewing key changes from PCIe Gen5 and the impact of PAM4 signaling on system and test. We concluded with a discussion of the impact of PAM4 signaling on system and test and PAM4 in electrical Ethernet IEEE 802.3ck.

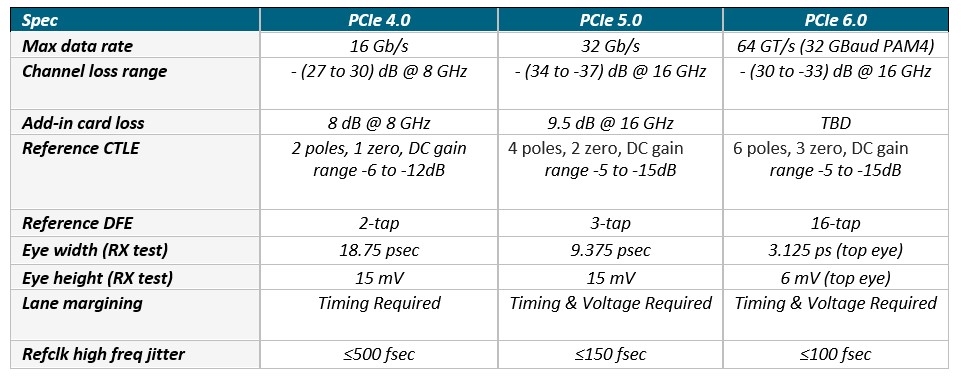

Figure 1. PCI Express Rate Electrical Evolution. Compare the GT in PCIe to GB vs Gb/s in Ethernet.

The table (Figure 1) above shows the evolution of PCI Express from 4.0 to 5.0 and then to 6.0 and some of the key attributes for the physical layer. There’s been a doubling of the data rate starting at 16 gigabits per second to 32, and now to 64, which is the first multi-level at PCI Express 6.0 using PAM4 signaling. You can also see the eye height was consistent from PCIe Gen4 to Gen5, but now it’s at 6 millivolts for Gen6, although a lot of this is still under development and not yet finalized. There is a considerable increase in complexity as you move to the multi-level signaling with many new considerations for PCI Express.

In terms of the timeline to PAM4 Ethernet, everything high speed electrical was NRZ until 2017 when the new 26 GBd standard came out, 50 gigabit in the optical front and 50 gigabit in back interconnect. Now, in optics, it's actually relatively doable to double the speed, and that happened very quickly. In fact, the first PAM4 spec already had the simplest optics running also at 53 GBds, so-called DR4, and there was no back interconnect for it. So you had to use two electrical lanes to back it up. Adjusting for electrical, it wasn't filled with CK work where now we are trying to get the Ethernet to operate on a 53 GBd or 100 giga per differential lane.

As looked at the evolution and timeline of PCIe, we also covered a number of other topics, including:

- The testing of receivers – how it looks for Ethernet, signal detection and error rate

- Calibrating the stress eye signal

- Spread spectrum clocking (SSC) – both enabled and disabled, and the experimentation completed

- Methodology changes between PAM4 26 GBd and 53 GBd electrical signaling

- Comparison in patterns

- Comparison in jitter/noise measurements

- Examining tools for measuring Ethernet and PCIe 6.0

We conclude by stating that while the standards are closer than in the past, key differences still remain. Yes, both standards have moved to PAM4 and there are now speeds above 26 GBd; about 50 giga per lane. There are similarities in several places, for example SNDR, as well as some differences in patterns, details of jitter and noise measurements, and the way we handle the return loss. There are tools for each standard as well that are discussed at length.

Consider watching our full discussion here or viewing Tektronix’ PCI Express solutions here. For a further discussion of what may lie ahead with PCI Express, Gen 6, view our recent webinar, Exploring Future Measurement Methodologies for PCI Express 6.0 PAM4 Signaling.

PCIE and PCI-SIG are registered trademarks and/or service marks of PCI-SIG.