Contact us

Call us at

Available 6:00 AM – 5:00 PM (PST) Business Days

Download

Download Manuals, Datasheets, Software and more:

Feedback

Gain deeper timing insight across a wide range of applications with Advanced Jitter Analysis software (opt. DJA). Available on the 5 Series B MSO, 6 Series B MSO, and 7 Series DPO oscilloscopes, DJA delivers powerful jitter, eye diagram, and timing analysis for everything from low-speed embedded clocks to high-speed serial interfaces. From serial links to clocks and PLLs, DJA helps you uncover jitter sources, debug faster, and validate performance with confidence.

Learn:

- Jitter Analysis for Validation and Debug Workflows

- How to identify and solve jitter issues

- How to break down total jitter into its components for root cause analysis

- Industry-leading visualization tools to debug jitter issues and validate signal integrity

- How Tektronix jitter results are grounded in industry standards

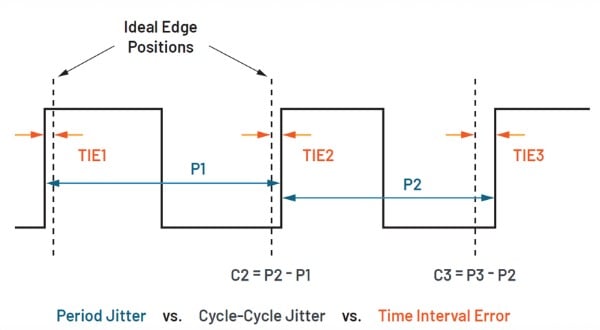

Different fundamental jitter measurements

Jitter Analysis for Validation and Debug Workflows

Jitter is the unwanted variation in signal timing that eats away at signal integrity. In high-speed systems, even subtle timing shifts can collapse eye diagrams, introduce bit errors, and push designs out of spec. Whether from power noise, crosstalk, reflections, or clock instability, jitter threatens your USB, PCIe, DDR, and Ethernet designs—impacting performance and reliability.

How to Identify and Solve Jitter Issues

If you see eye closure, data errors, or clock issues, jitter analysis isn’t optional—it’s critical. Tektronix offers precise tools like eye diagrams, TIE plots, and jitter decomposition to isolate root cause and ensure timing margins are met.

How to analyze and debug jitter:

- Acquire DUT signal with adequate oscilloscope bandwidth and probe

- Run jitter analysis with just a few clicks using DJA software (opt. DJA)

- Configure clock recovery to mimic system under test behavior

- Perform TIE, eye diagram, jitter bathtub, and spectrum analysis.

- Decompose Total Jitter

- Correlate jitter with likely root causes

- Make fixes and re-test

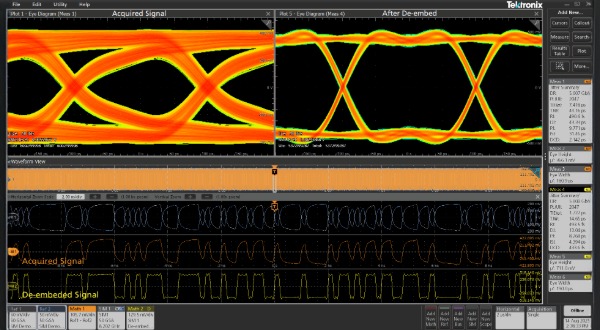

- De-embed, embed, or use equalization using SIM software (opt.SIM)

- Adjust EQ, layout, power, or component selection

- Re-acquire and re-analyze to confirm improvement

- Document everything for traceability and compliance

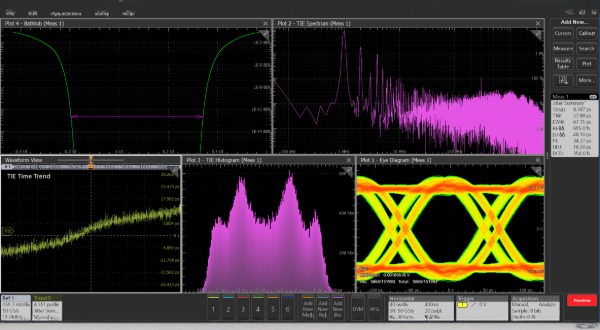

Jitter analysis reveals a 2.5 Gb/s link with dominant periodic jitter at ~125 MHz, significant DDJ from ISI, and measurable DCD—pointing to clock or power-supply coupling as likely root causes.

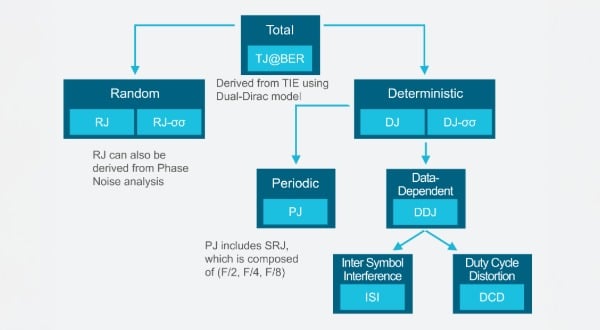

Break Down Total Jitter into its Root Components

Jitter decomposition helps identify root causes and apply targeted fixes—like optimizing clock sources, adjusting equalization, or improving layout.

Tektronix Advanced Jitter Analysis (opt. DJA) software helps you isolate jitter. With only a few clicks, determine Total Jitter (TJ), through detailed analysis of:

- Random Jitter (RJ): Noise-like, unbounded

- Deterministic Jitter (DJ): Predictable, bounded (like periodic jitter)

- And subcomponents (PJ, DDJ, ISI, DCD, etc.)

Learn more about isolating, analyzing, and addressing jitter

Industry-leading Visualization Tools

Tektronix' advanced jitter analysis software (opt DJA) is designed to give you deep insight into signal behavior.

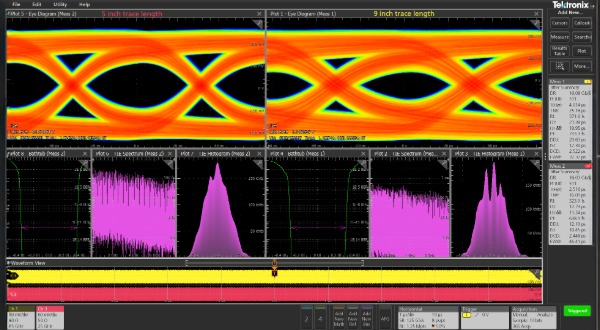

- Tektronix uniquely supports virtually unlimited parallel measurements and plots—each with independent clock recovery settings—for rapid side-by-side comparisons of equalization strategies, margin sensitivity, or configuration changes.

- Multiple interactive plots—including eye diagram, histogram, bathtub curve, spectrum, and more—within a single, integrated UI for enhanced insight.

- Real-time Eye-diagram rendering to reveal timing, noise, and distortion with user-definable PLL emulation — all at once.

- Eye-diagram metrics like Eye Height, Eye Width, Eye@BER, Eye High/Low, and Q-Factor to quantify signal margin and enable predictive BER analysis.

- Comprehensive eye mask testing, including auto-fit and margin visualization, for standard-compliant validation across a wide range of serial standards.

Explore Advanced Jitter Analysis (DJA) oscilloscope software

Rapid side-by-side comparison of a 5-inch trace versus 9-inch

Trusted Jitter Analysis, Grounded in Industry Standards

Tektronix jitter, eye‑diagram, and timing analysis tools are designed with the same core innovations that defined the industry—backed by patented real‑time clock recovery, eye rendering, and spectrum‑based jitter decomposition techniques. Trusted and certified by PCI-SIG, USB, and other leading industry bodies.

Tektronix jitter and timing measurements are built on the same proven algorithms used in our industry-standard DPOJET software—ensuring consistency, trust, and continuity for long-time users.

Correlation is routinely validated through participation in plugfests, compliance workshops, and internal comparison tests—helping ensure our results align with industry methods and expectations.