연락처

텍트로닉스 담당자와 실시간 상담 6:00am-4:30pm PST에 이용 가능

전화 문의

9:00am-6:00PM KST에 이용 가능

다운로드

매뉴얼, 데이터 시트, 소프트웨어 등을 다운로드할 수 있습니다.

피드백

자동 테스트 및 디버깅

고속 디지털 표준은 데이터 중심 세계의 성능 요구를 지원하기 위해 빠르게 진화하고 있습니다. 차세대 직렬 표준과 데이터 통신 요구 사항은 오늘날의 컴플라이언스와 디버그 도구의 한계를 뛰어넘는 새로운 테스트 과제를 제시하고 있습니다. 설계에서 시뮬레이션, 분석, 디버그와 컴플라이언스 테스트에 이르기까지, Tektronix는 성능을 최적화하고, 검증 주기를 가속화하며 시장 출시 기간을 단축하는 자동 전기 테스트 솔루션을 제공합니다.

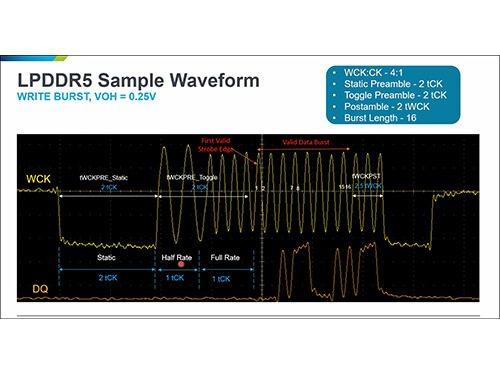

고성능 연산 표준의 정확하고 반복 가능한 테스트

데이터 센터, 인공 지능(AI) 및 고성능 연산과 같은 데이터 집약적 시장에서는 더 큰 데이터 처리량과 메모리 용량 증가에 대한 요구가 계속해서 증가하고 있습니다. 더 높은 데이터 전송 속도는 신호 무결성의 한계를 넓히고 컴플라이언스, 디버깅 및 검증에 대해 고성능의 측정 기능이 요구되는 복잡한 설계로 이어집니다. Tektronix의 자동 테스트 솔루션은 엔지니어들이 이러한 과제를 정확하고 반복적으로 해결함으로써 최신 설계를 테스트할 수 있도록 지원합니다.

소비자 기술 테스트 시간 감축

혁신의 속도는 더욱 새롭고 빠른 소비자 장치에 대한 수요를 자극하고 있습니다. 그 개발의 기본이 되는 표준은 증가된 데이터 속도와 설계의 복잡성 측면에서 새로운 테스트 과제를 제시합니다. Tektronix 테스트 솔루션은 최신 사양에 맞게 정확하고 반복 가능한 측정을 제공하며 테스트 시간을 단축합니다.

이더넷 장비 설계용 종합 도구

이더넷은 대규모 데이터 센터와 엔터프라이즈 시스템에서 자동차와 산업 애플리케이션에 이르는 네트워크 연결을 제공합니다. Tektronix는 이러한 생태계에서 IEEE 802.3 이더넷 장치의 물리적 계층을 테스트하고, 개발하고, 디버깅하기 위한 종합 도구 세트를 제공합니다.

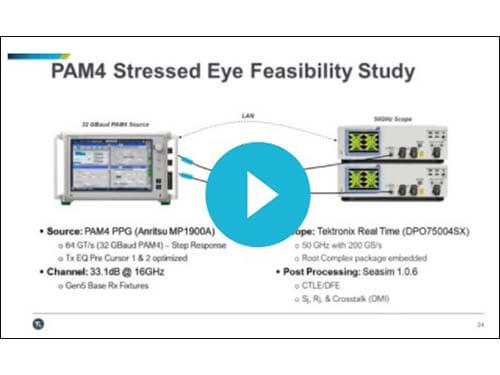

고급 측정 및 분석 도구

Tektronix의 SDLA, PAMJET 및 DPOJET 소프트웨어는 고속 직렬 표준을 위한 강력한 신호 분석 도구를 제공합니다. PAMJET을 사용하여 최신 PAM4 신호를 분석하든, SDLA로 파형을 디임베딩하든, DPOJET으로 지터/노이즈 분석을 수행하든 Tektronix는 사용자에게 필요한 도구를 제공합니다.